2026 先進封裝指南(三):Chiplet 封裝與異質整合技術解析

我們在上一篇文章中詳述的先進封裝架構,不僅僅是製造技術而已;它們是實現系統設計更宏大革命的物理基石。本文將聚焦於這一戰略轉變。我們將透過定義什麼是小晶片 (chiplets)以及為何它們如此具有優勢,來探討當前邁向解構的設計趨勢。

接著,我們將解釋異質整合的力量——即靈活混合搭配這些小晶片的藝術——並詳述 Universal Chiplet Interconnect Express (UCIe) 標準在建立未來開放式、隨插即用 (plug-and-play) 生態系中所扮演的關鍵角色。

3.1 轉向解構:什麼是小晶片?

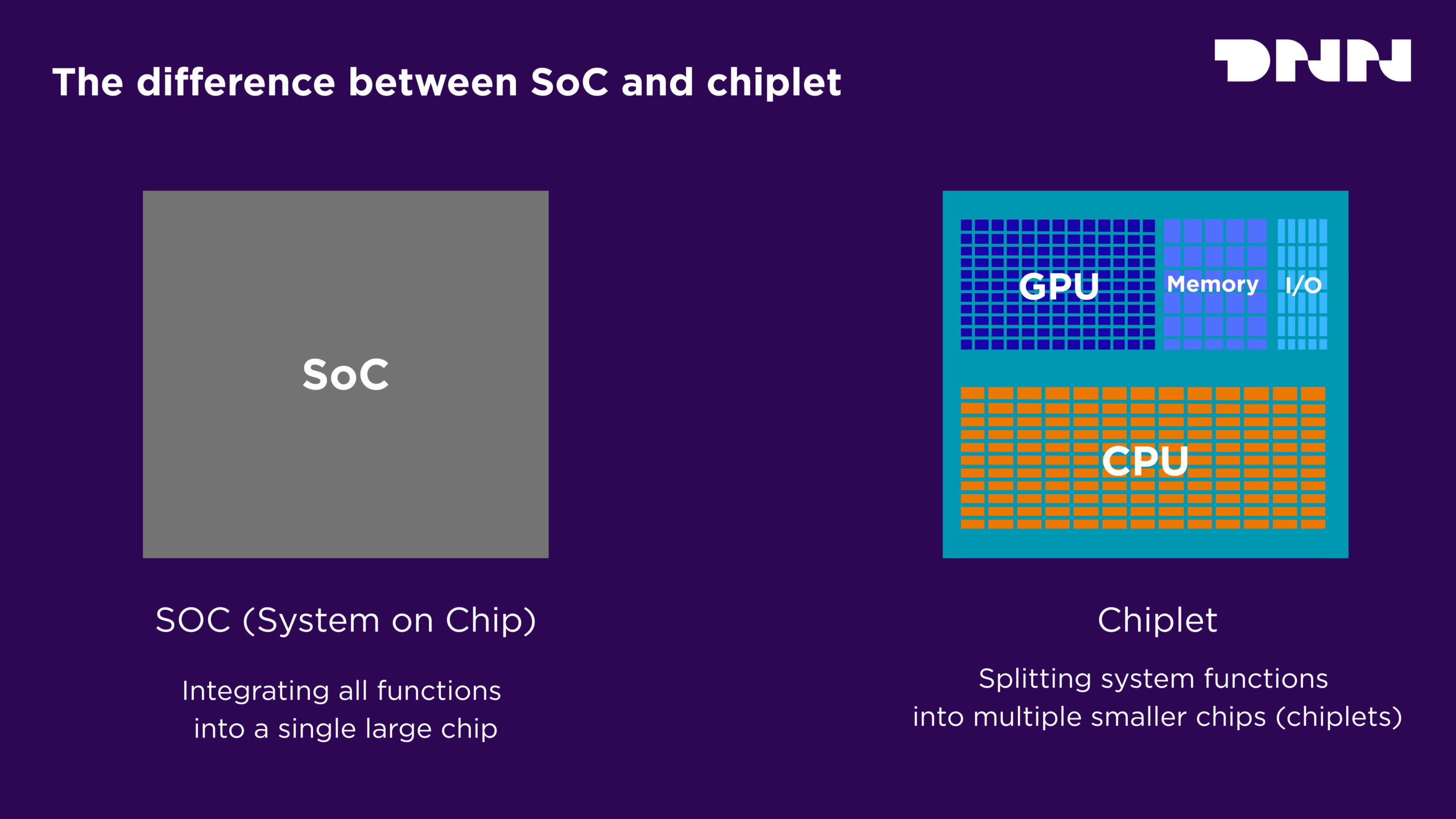

就其核心而言,小晶片 (Chiplet) 的概念代表了從單體式設計轉向解構的重大變革。

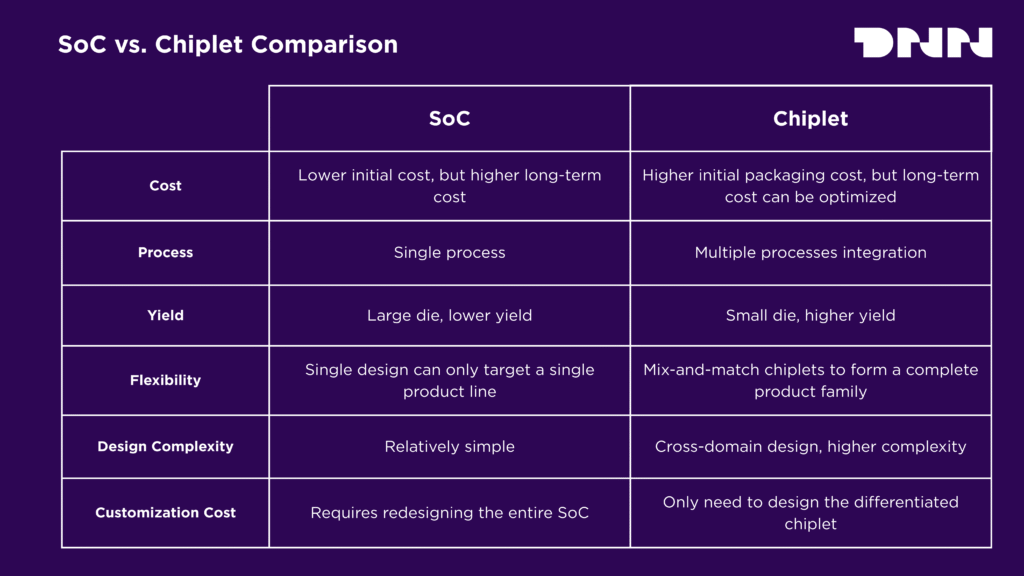

最好不要將 Chiplet 僅僅視為一顆小晶片,而應將其視為一種全新的設計哲學。它是一顆未封裝的晶粒 (unpackaged die),一個獨立的功能區塊,經過專門設計與優化,以便能與其他 Chiplets 結合並共同封裝,進而組成一個規模更大、更複雜的系統。

這種方法有效地將一顆大型的單體式系統單晶片 (SoC) 分解為其各個組成部件,例如 CPU 核心、I/O 控制器以及記憶體介面。

小晶片 (Chiplet) 的定義在業界仍處於演變階段,這正是此領域發展迅速的標誌。

部分專家主張,” 其關鍵特徵在於擁有專用且標準化的晶粒間 (die-to-die) 通訊介面。其他人則強調協同設計的層面,意即一組晶粒從一開始就被設計為作為一個單一、緊密的系統共同運作,而不論其使用何種特定介面。 “

無論精確定義為何,這種解構式方法的效益都是顯而易見且具說服力的:

提升製造良率並降低成本

大型的單體晶片出現製造缺陷的機率較高,一旦出現缺陷往往導致整顆晶粒報廢。透過將系統拆解為較小的 Chiplets,每個個別元件的良率將大幅提升。這允許製造商僅採用已知良品裸晶 (Known-Good-Die, KGD),從而顯著降低整體成本。

此外,這種方式允許針對每一種功能採用最適切且具成本效益的製程節點,而非強迫將所有功能都移至最昂貴的先進節點上製造。

加速上市時間與設計重用

一旦 Chiplet 完成設計與驗證,它就成為一個可重複使用的模組,就像軟體資料庫中的一項矽智財 (IP) 一樣。例如,一個經過驗證的 I/O Chiplet 可以被整合到多個不同的產品線中,僅需極少的重新設計工作。這能加速開發週期,並將初始的一次性工程費用分攤到多項產品之上。

強化可擴展性與靈活性

基於小晶片 (Chiplet-based) 的設計允許透過混合搭配不同的小晶片來創造完整的產品系列。一家公司可以提供搭載 8 個 CPU 小晶片的高階伺服器處理器,以及搭載 4 個的主流版本,且兩者皆使用相同的 I/O 與記憶體小晶片,提供了巨大的靈活性。

小晶片的興起正在半導體設計領域創造一個新的、強大的抽象層,這類似於歷史上從電晶體層級 (transistor-level) 設計轉向在暫存器傳輸級 (Register-Transfer Level, RTL) 設計中使用可授權 IP 區塊的轉變。

在過去,打造客製化 SoC 是一項艱鉅且昂貴的工程,僅限於擁有龐大資源的大型企業才能實現。

小晶片是 IP 重用概念的實體展現,具有將客製化晶片設計普及化的潛力。在未來,一家公司理論上可以從供應商 A 購買 CPU 小晶片,從供應商 B 購買 AI 加速器,並從供應商 C 購買標準 I/O 小晶片,然後將它們整合為一個針對特定市場量身打造的獨特系統。

這種隨插即用模式大幅降低了進入門檻,使規模較小、更靈活的公司能夠將資源集中在設計單一、具差異化優勢的小晶片上,同時以現成的方式採購其他必要組件。

這種技術移不僅是為了提高大公司的良率;它更有潛力成為催化劑,引發來自更廣泛參與者的新一波創新浪潮,根本性地改變誰可以設計和構建客製化晶片的生態。

3.2 異質整合:混合搭配的藝術

異質整合是小晶片 (chiplet) 設計哲學的實際應用與終極目標。其定義為將多個、相異的半導體元件組裝進單一封裝之中。這些元件之所以被稱為「異質」,是因為它們可以在功能(如邏輯 logic、記憶體 memory、射頻 RF、類比 analog)、製造製程技術(例如 5nm 對比 28nm),甚至在生產它們的晶圓代工廠 (foundry) 或供應商方面有所不同。

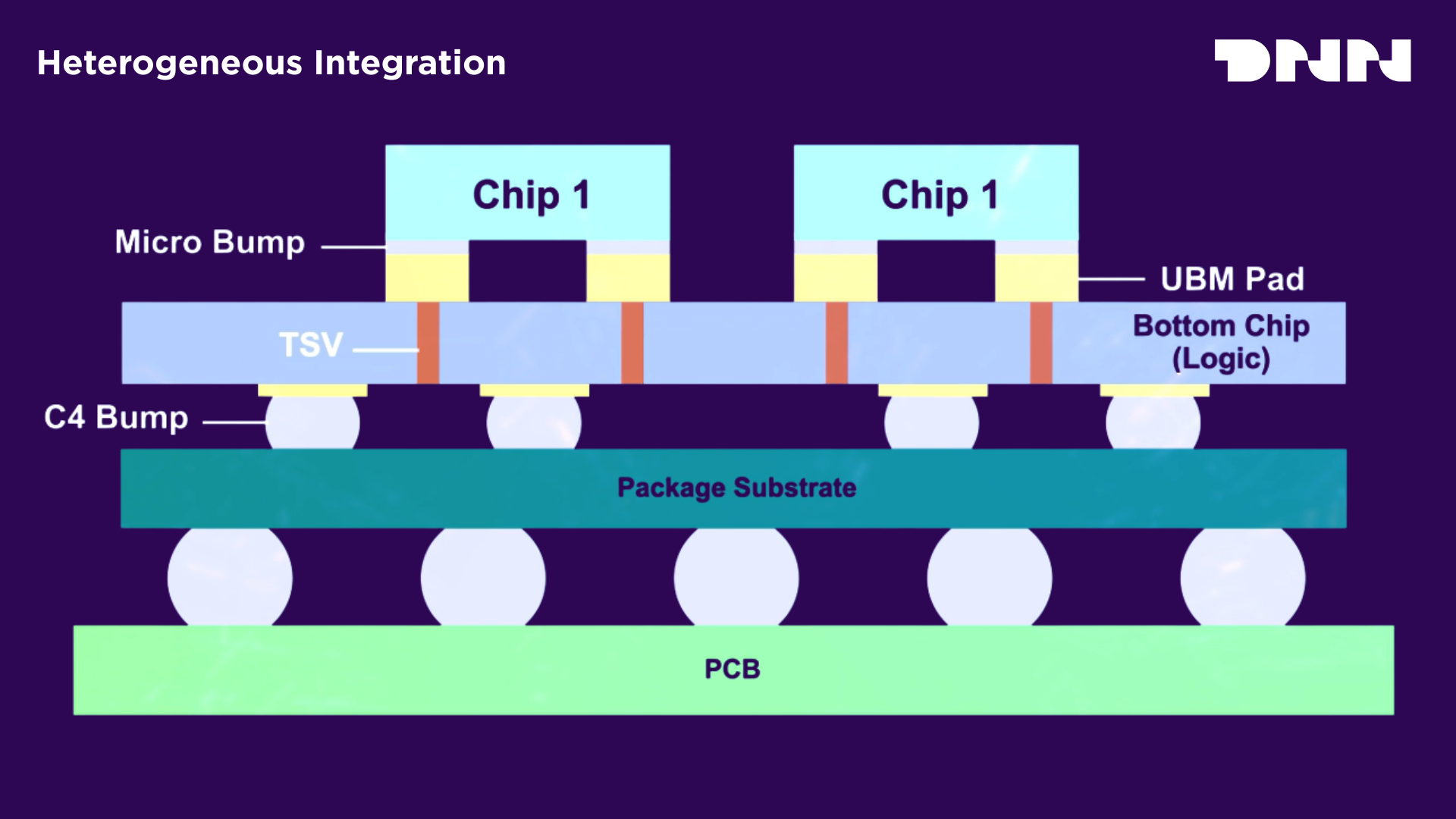

我們先前討論過的先進封裝架構——2.5D、3D 以及 FOWLP——正是讓這種精密混合搭配方法得以實現的物理平台。

異質整合標誌著過去主導單體式 SoC (monolithic SoC) 設計那種一體適用方法的終結。它實現了系統層級前所未有的優化水準。

單體式 SoC 本質上是一種妥協的設計;其製造製程通常是為了高效能數位邏輯而優化,但這對於敏感的類比電路、高壓電源管理或專用的 RF 元件之需求而言,往往並非理想選擇。

異質整合打破了這些妥協。它允許設計者針對每一項任務使用絕對最佳的技術。CPU 核心可以在先進的 3nm 製程節點上製造,以獲得最大的效能與效率。

類比 I/O 小晶片則可以建立在成熟的 28nm 製程節點上,提供優越的訊號特性與較低的成本。高頻寬記憶體可以使用其自身高度專業化的 DRAM 製程來生產。甚至像用於光學 I/O 的矽光子等新興技術,也能與傳統電子元件整合在一起。

因此,最終的整合系統不僅僅是各個部分的總和;它是一個具綜效的整體,在效能、功耗與成本上都能超越等效的單體式晶片,因為每一個單獨的元件都在其理想的技術平台上經過了個別優化。這實現了過去無法企及的系統級效能水準。

3.3 建立共同語言:通用小晶片互連 (Universal Chiplet Interconnect Express, UCIe)

為了充分實現基於小晶片、異質整合生態系的潛力,需要一項關鍵的基礎設施:標準化 。

若缺乏一套共通、開放的標準來規範不同供應商的小晶片如何彼此通訊,那麼隨插即用的願景將僅侷限於大型、垂直整合公司的專有封閉生態系之中。

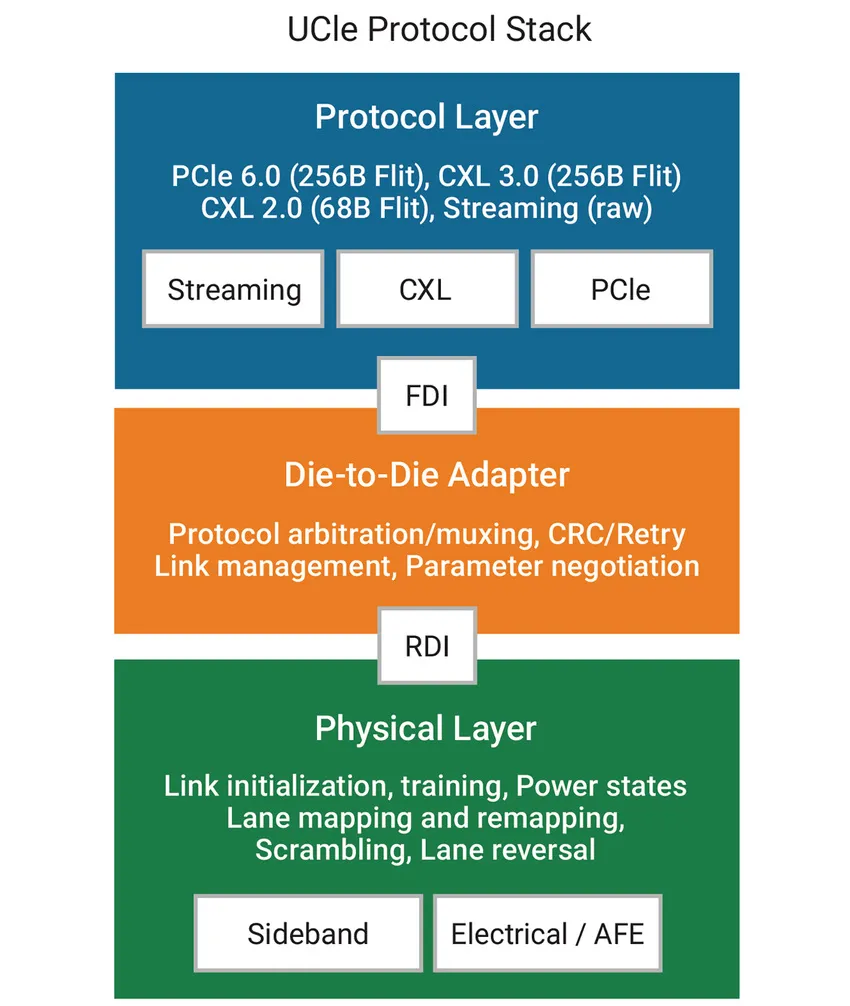

通用小晶片互連 (Universal Chiplet Interconnect Express, UCIe) 正是業界應對此挑戰的解答。UCIe 是一項開放式規範 (open specification),定義了完整的晶粒對晶粒 (die-to-die) 互連標準,涵蓋了讓小晶片能在封裝內彼此通訊所需的 I/O 實體層 (physical layer)、協定堆疊 (protocol stack) 以及軟體架構 (software framework)。

為了加速市場採用並確保廣泛的相容性,UCIe 標準巧妙地利用了成熟且經業界驗證的協定,如 PCI Express (PCIe) 與 Compute Express Link (CXL),作為其主要的通訊方式。

UCIe 可以說是這場小晶片革命中,單一最重要的非技術性催化劑。它的目標是成為小晶片界的 USB (USB for chiplets)

正如同 USB 標準為電腦外部周邊的連接創造了一個無所不在、具互操作性的生態系,UCIe 也致力於為封裝內互連 (on-package interconnects) 實現相同的目標。

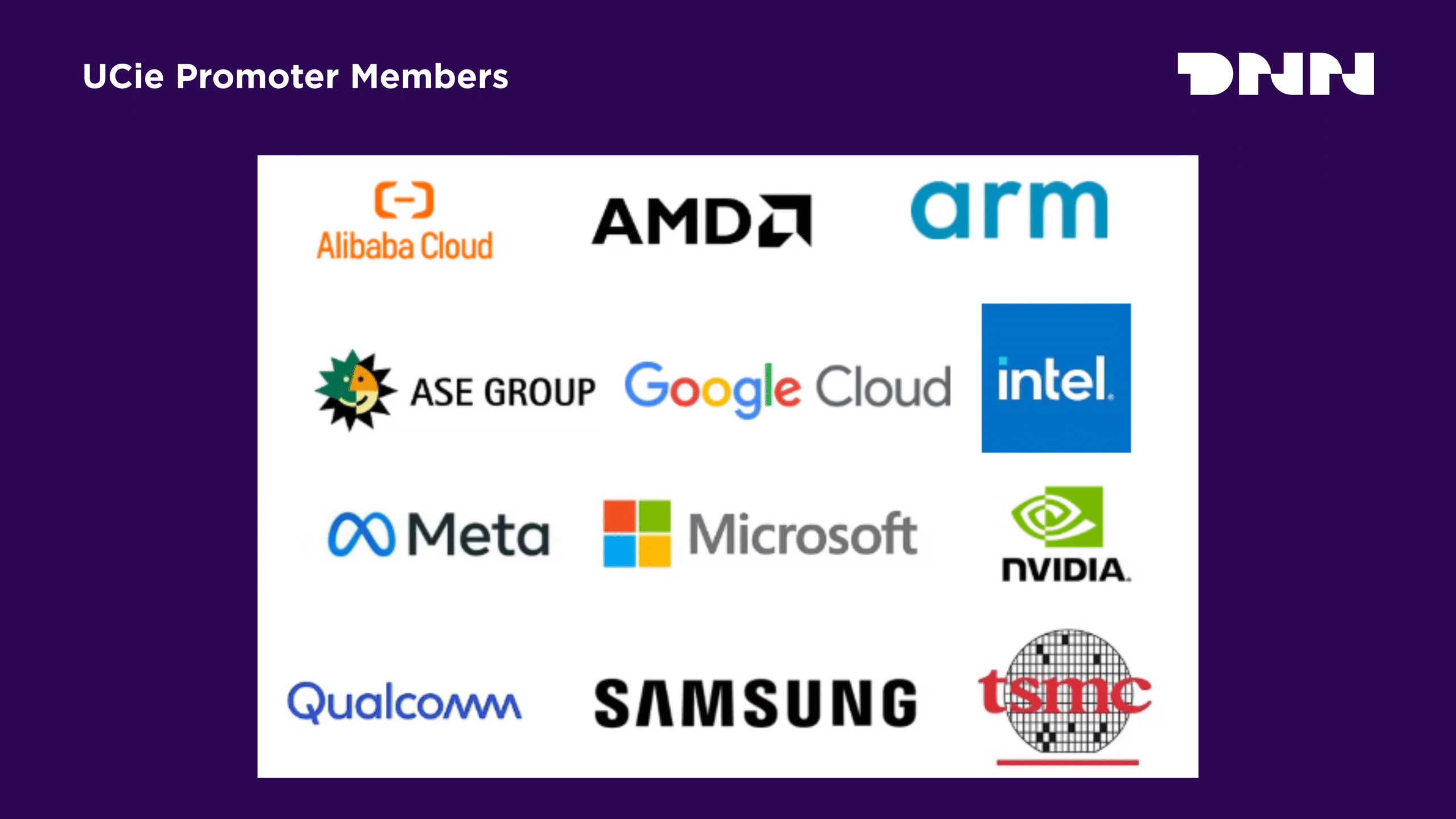

該標準是由一群產業領袖組成的聯盟所建立,成員涵蓋晶圓代工廠、IP 供應商、無晶圓廠 IC 設計公司以及雲端服務供應商。他們都深刻體認到,一個封閉且破碎的市場將會扼殺產業的創新。

透過建立一個標準化的插座 ,UCIe 賦予了系統設計者從多家不同供應商採購小晶片的信心,因為他們深知這些元件將能無縫地進行通訊。這正是解鎖小晶片典範所描繪的那個開放、具競爭力市場的關鍵鑰匙。

UCIe 的成功與否,很可能將決定小晶片究竟會繼續作為產業巨頭的專用工具 ,還是能成為一種普及化的資源,激發來自各種規模企業的新一波客製化晶片創新浪潮。它本身與其說是一項技術,不如說是一個基礎性的經濟與生態系賦能者。

關於 DNN Technology

總部位於台灣,DNN Technology 是半導體設備與全方位解決方案的全球領導者,專注於二手半導體設備交易 (Used Equipment Trading)、實驗室與無塵室系統建置 (Laboratory and Cleanroom Systems Construction) 以及技術顧問服務。

憑藉超過二十年的產業經驗與由三十多位資深技術專家組成的團隊,DNN Technology 已在五十多個國家成功執行專案,致力於提供客製化、創新且高效的解決方案。