2026 先進封裝指南(四):解決散熱挑戰與中介層材料(Si/Glass/Organic) 比較

前言

先進封裝所展現的卓越能力並非魔法,而是建構於材料科學與物理學的複雜基石之上。將多個高功率元件擠壓至微觀空間中,創造出一個緊密耦合的系統,其效能表現完全受制於基礎物理力的運作。

本文將深入探討這背後的科學原理。我們將剖析中介層材料的關鍵角色——分析矽 (silicon)、有機 (organic) 與玻璃 (glass) 之間的權衡取捨——並解釋為何採用全方位的多物理場協同設計方法不再只是選項,而是駕馭熱、電與機械複雜交互作用的必要手段。

4.1 中介層的兩難:深入剖析材料科學

中介層 (interposer) 是 2.5D 整合技術的中樞神經系統,其材料的選擇決定了效能、成本與可製造性 之間最根本的權衡取捨。並不存在單一的「最佳」材料;取而代之的是,一個多元化的材料工具箱正在成形,以滿足特定的應用需求。

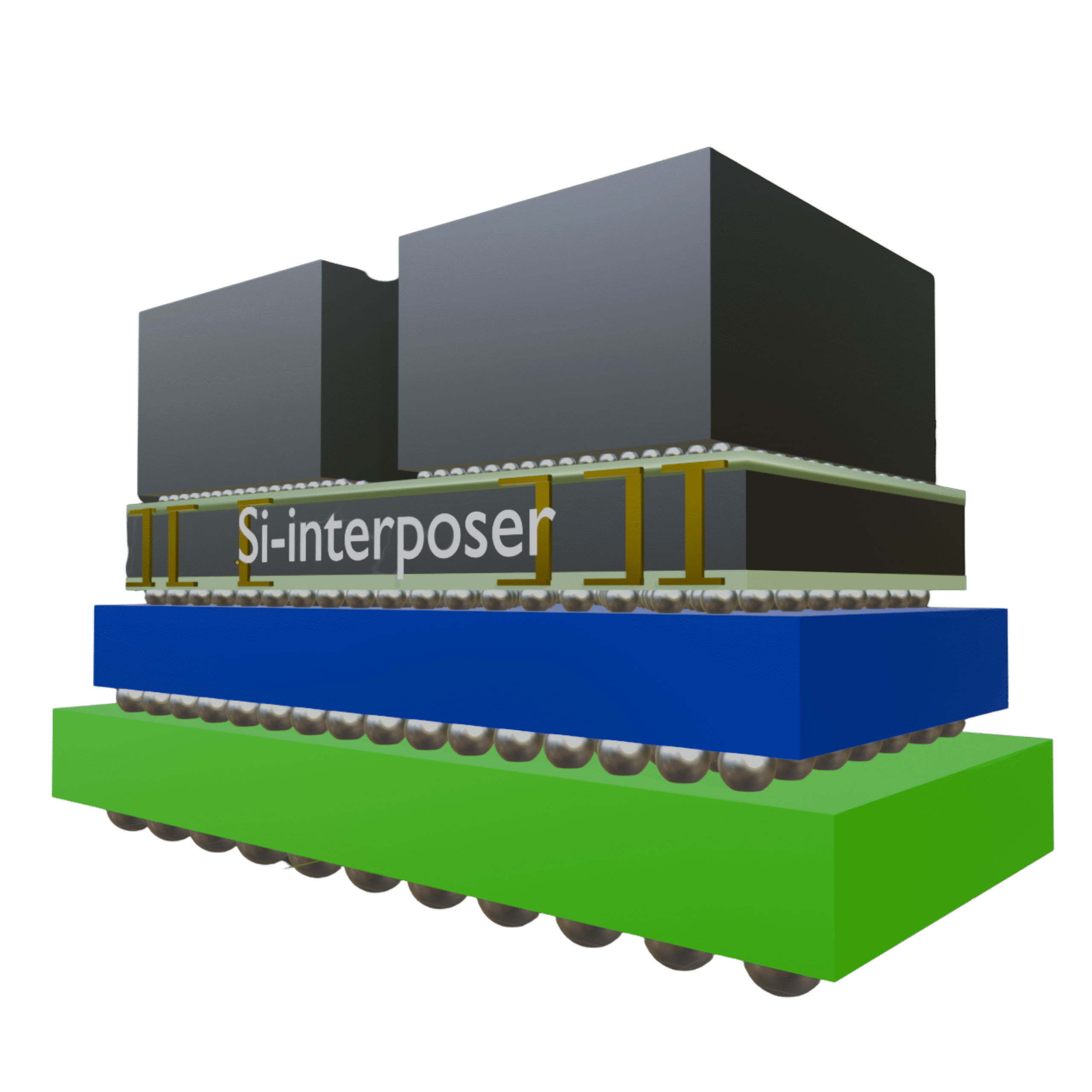

- 矽(Si)中介層

作為高效能應用的現行主流技術,矽中介層利用成熟的 CMOS 製程,提供無與倫比的佈線密度(線寬/線距 L/S < 1μm)。其約 3 ppm/°C 的熱膨脹係數 (CTE) 與矽晶粒完美匹配,從而將應力降至最低。

這項技術是 TSMC CoWoS 等領先解決方案的基礎,並被應用於 NVIDIA H100 GPU 中,該產品在單一矽中介層上整合了強大的 GPU 與多個高頻寬記憶體 (HBM) 堆疊。然而,其約 11.9 的高介電常數 (Dk) 可能會阻礙高速訊號的傳輸,且與大面積矽片相關的高昂成本是一大顯著缺點。

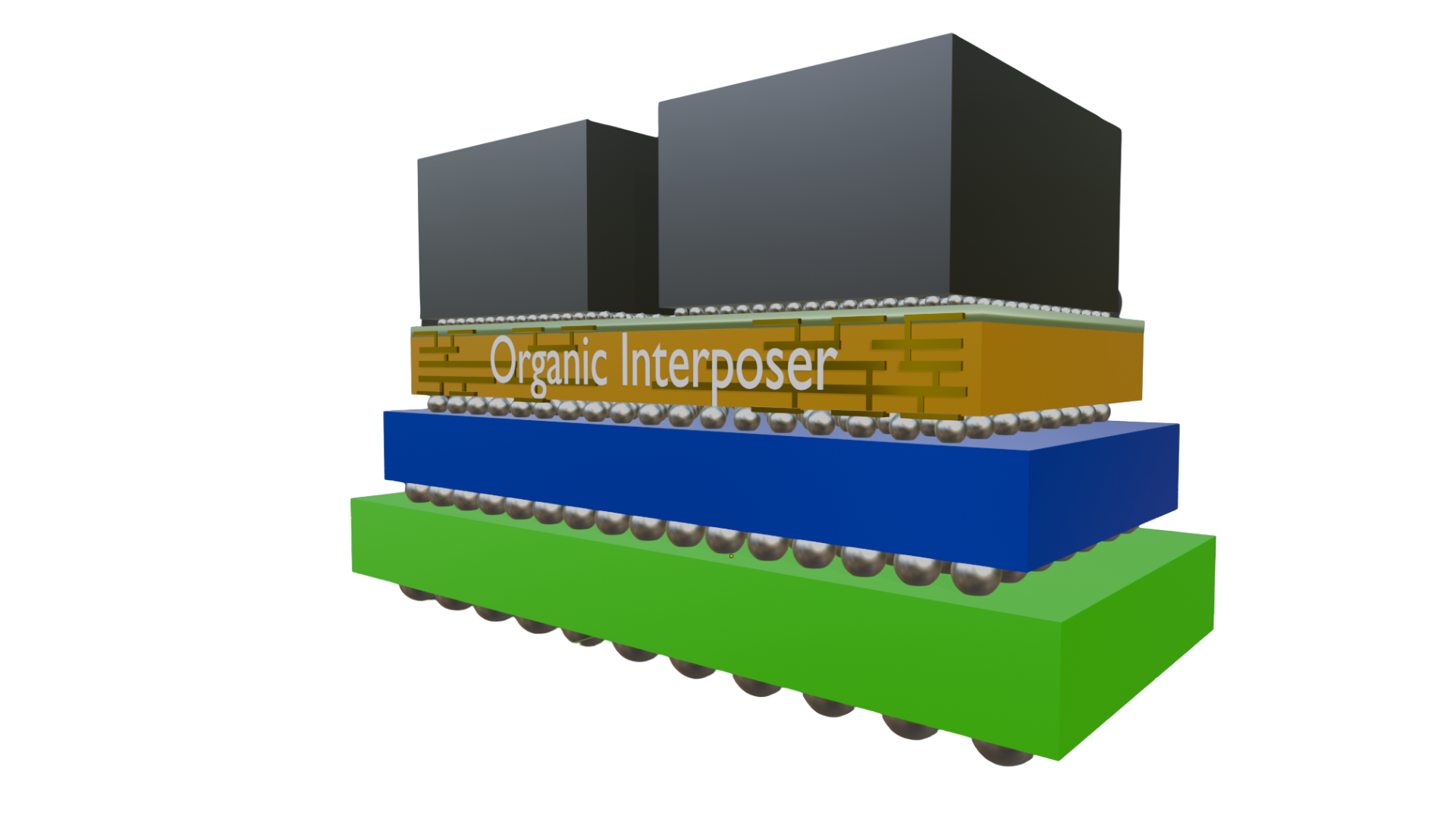

- 有機中介層

作為一種具成本效益的替代方案,有機中介層正獲得越來越多的關注。如液晶高分子等材料提供了較低的介電常數 (約 3.1),這對訊號完整性極為有利。

它們更具彈性,且可以在更大、更經濟的面板上製造。然而,其佈線密度較低 (線寬/線距約 2-4μm L/S);更關鍵的是,它們與矽之間存在嚴重的熱膨脹係數 (CTE) 失配 (約 17-50 ppm/°C),這是導致封裝翹曲 (package warpage) 與可靠度問題的主要根源。

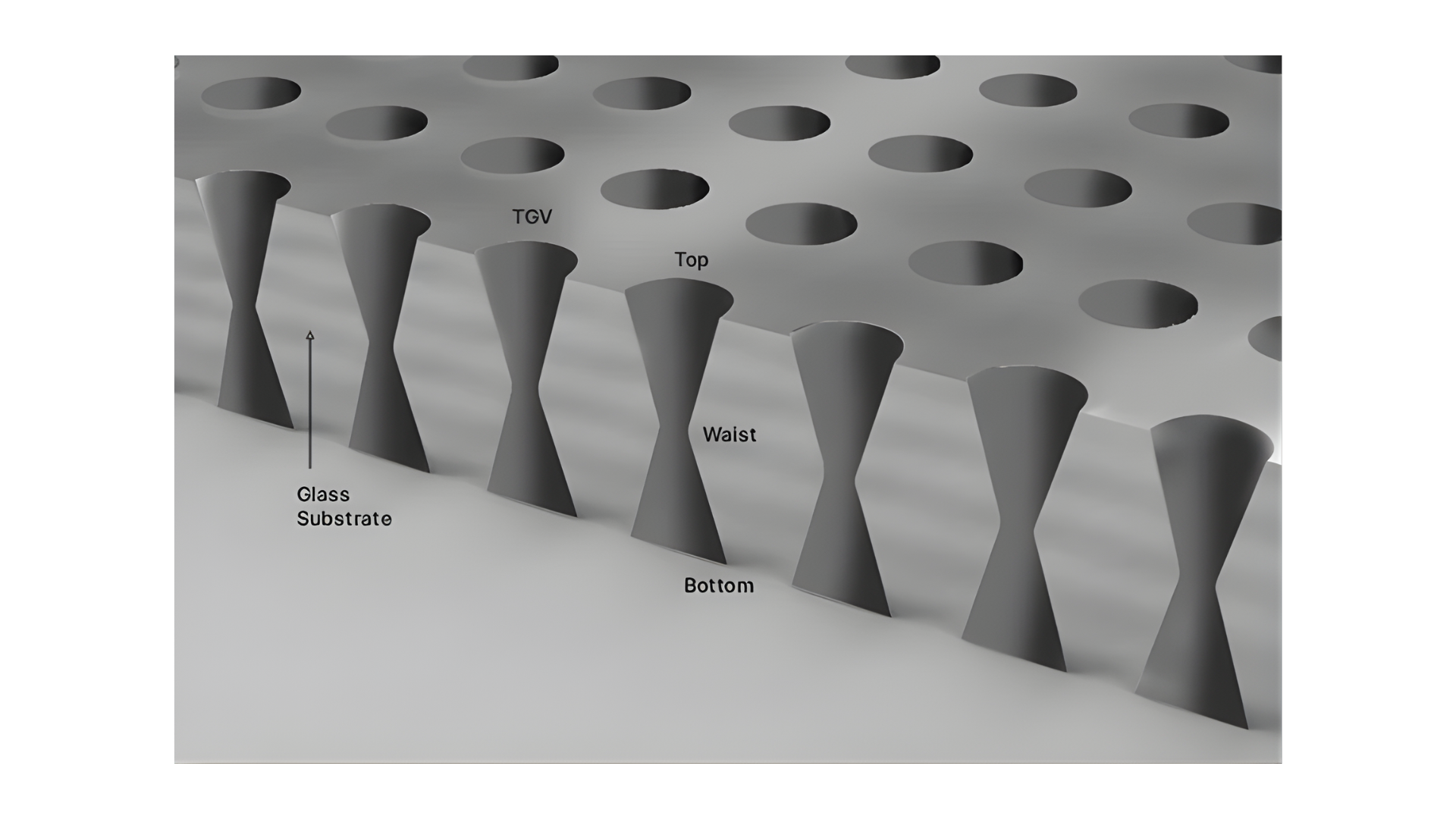

- 玻璃中介層

玻璃代表了一條極具前景的未來路徑,有望提供一種集各家之長的解決方案。它結合了卓越的尺寸安定性與較低的介電常數 (約 4-6),且其熱膨脹係數 (CTE) 可透過工程手段調整至與矽匹配 (約 3-8 ppm/°C)。

預計到 2032 年,該市場規模將超過 24 億美元。包括 Intel、Samsung、Corning (康寧) 與 AMD 等主要大廠正積極投資並申請專利,以解決製造上的挑戰。目前的主要障礙在於製造生態系尚未成熟,特別是高深寬比 的玻璃穿孔 (Through-Glass Vias, TGVs) 之製程,其成本高昂且良率偏低。

資料來源: Semiconductor Engineering

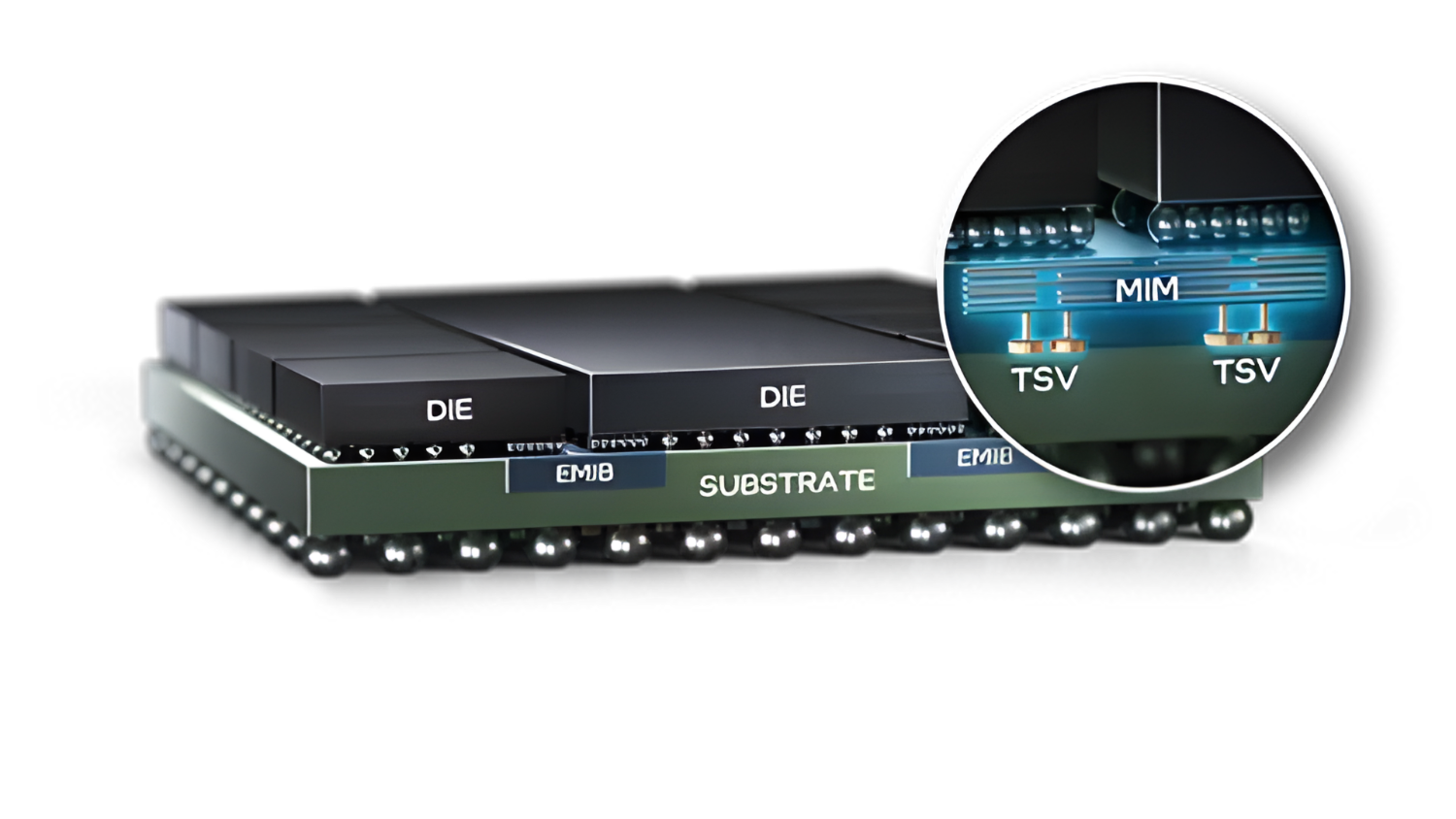

- 嵌入式多晶粒互連橋接 (EMIB) 解決方案

像 Intel 的嵌入式多晶粒互連橋接 (EMIB) 這樣的技術提供了一個巧妙的折衷方案。它不使用大面積且昂貴的矽中介層,而是將小型、高密度的矽橋接器直接嵌入成本較低的有機載板中,並精確地配置在需要高頻寬晶粒間通訊的特定位置。

這種方法已被應用於如 Ponte Vecchio GPU 等產品中。它成功地將矽材料的優勢局部化,同時利用了有機載板在成本與可擴展性上的優勢,代表了半導體產業邁向混合材料解決方案的一個關鍵趨勢。

(資料來源: Intel)

這種材料選擇的兩難不僅僅是技術上的權衡;它引發了一連串從物理學延伸至經濟學的因果鏈。AI 加速器的效能需求,決定了其邏輯晶粒與 HBM 之間必須具備極高的互連密度。這種密度要求將設計推向了矽中介層 (silicon interposer),因為有機材料無法達到所需的 <1µm 線寬/線距 (line/space)。

然而,選擇大面積的矽中介層並將其與有機封裝載板結合,會引入巨大的 CTE 失配。這種失配會產生顯著的熱機械應力,導致封裝翹曲與錫球接點可靠度成為主要的失效模式。

這種可靠度風險反過來又迫使業者必須在多物理場模擬工具 (multi-physics simulation tools/EDA) 與先進熱介面材料 (TIMs) 上投入鉅資,以緩解應力並管理熱量。

因此,最初由效能驅動的矽中介層選擇,直接導致了重大的可靠度挑戰,進而驅動了對緩解技術的經濟投資。這揭示了在先進封裝領域中,材料科學、物理學與經濟學是如何密不可分地連結在一起。

下表提供了關鍵中介層材料的比較分析,突顯了其中涉及的工程權衡:

4.2 看不見的敵人:駕馭熱機械應力

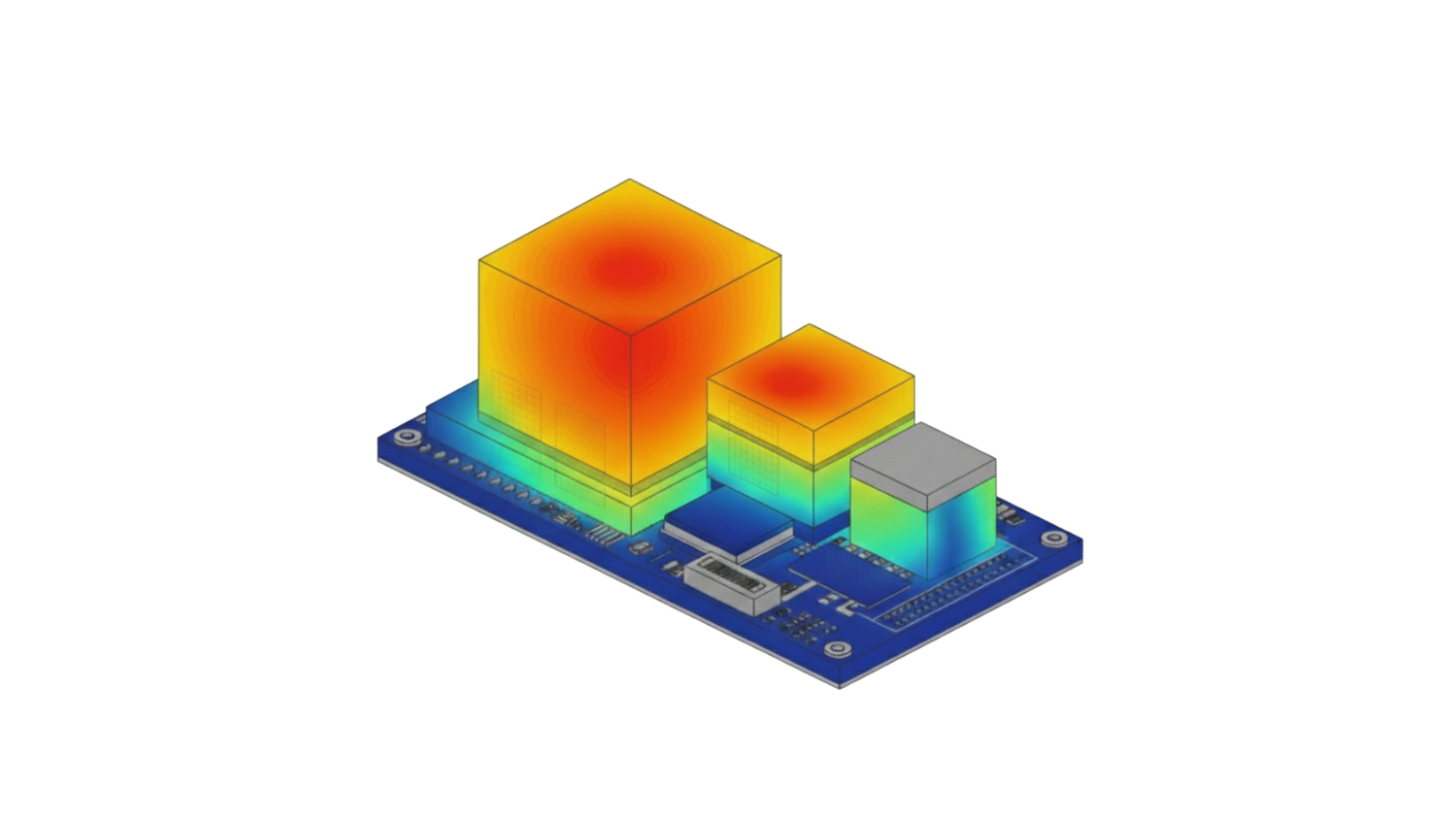

在先進封裝領域中,最無所不在的可靠度挑戰莫過於熱機械應力。這個問題的根源在於不同材料隨溫度變化而膨脹與收縮的方式存在根本性的不匹配。這絕非一個次要問題,而是一項可能導致災難性失效的首要設計限制。

- CTE 失配的物理機制:

在製造過程(如回焊 reflow)與實際運作期間,封裝體會經歷顯著的溫度循環。矽晶粒的膨脹率約為 2.6-3 ppm/°C,而標準的有機載板膨脹率則可能高達 17-50 ppm/°C。這種巨大的差異迫使元件發生彎曲與翹曲,進而產生極大的內部應力。這些應力會集中在最脆弱的環節:脆弱的錫球接點與互連結構上。

- 失效的後果

這種應力具體表現為封裝翹曲,這可能阻礙正確的安裝並導致開路。在反覆的熱循環下,它會引發金屬疲勞 (metal fatigue),導致錫球破裂以及層與層之間的分層,最終導致元件失效。由於大型矽中介層的尺寸因素,這個問題在大型 2.5D 封裝中尤為嚴重。

- 協同設計 (Co-Design) 的必要性

傳統那種把設計丟過牆就完事的線性設計流程已經過時了。由於電學、熱學與力學現象之間的緊密耦合 ,使得採用多物理場協同設計的方法成為絕對必要。

電氣活動會產生熱 (電熱效應 electro-thermal),熱會導致材料膨脹並引發應力 (熱機械效應 thermo-mechanical),而這種機械應力反過來會導致矽晶格變形,進而改變電晶體的電氣特性並影響時序

複雜的回饋迴路至關重要。這些工具讓架構師能夠在實際製造之前,就精準地預測並緩解應力問題。

4.3 散熱挑戰:先進熱管理解決方案

隨著 3D 堆疊與高密度 2.5D 系統中的功率密度急遽飆升,熱移除已成為最終的物理瓶頸。要從微觀體積中移除數百瓦的熱量,需要經歷一場從傳統冷卻技術轉向先進材料與破壞式創新技術的典範轉移。

- 熱介面材料 (TIMs) 的角色

TIMs 對於橋接晶粒 (die)、封裝蓋 (lid) 與散熱器 (heat sink) 之間的微觀空氣間隙 (air gaps) 至關重要。業界根據其應用位置將其分類為:TIM1 (晶粒對封裝蓋)、TIM1.5 (無蓋設計中的晶粒對散熱器) 以及 TIM2 (封裝蓋對散熱器)。雖然聚合物基 (polymer-based) TIMs 很常見,但高效能運算 (HPC) 領域正日益依賴效能更優越的金屬基 (metal-based) TIMs。

。 先進金屬熱介面材料:

這些材料包括焊料熱介面材料,它們透過形成直接的冶金結合來提供最低的熱阻;液態金屬,提供卓越的潤濕性 但需要小心的圍堵設計;以及可壓縮熱介面材料(如 Indium 公司的 Heat-Spring®),它們無須經過回焊製程即可提供高效能。

這些材料的熱導率(高達 86 W/mK)比傳統聚合物散熱膏高出一個數量級,這使其成為冷卻高功率 AI 加速器的關鍵技術。

資料來源: 歐耀科技

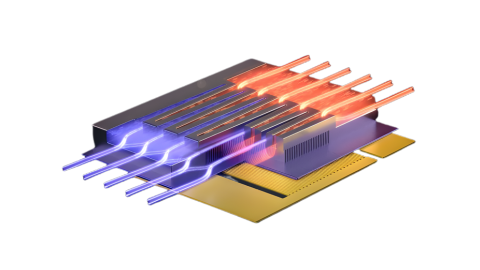

- 未來展望:直接液體冷卻與微流道冷卻

面對最極端的散熱挑戰,特別是在熱量容易受困於層與層之間的高密度 3D 堆疊中,傳統的氣冷技術已顯得捉襟見肘。未來的趨勢在於將液體冷卻劑直接引導至矽晶片上。微流道冷卻技術涉及將微觀通道直接蝕刻在矽晶粒的背面,讓冷卻劑能直接流經晶片本身。

來自 Microsoft 等公司的前瞻研究顯示,在特定測試條件下,這種方法的散熱效率可達先進冷板的 3 倍以上,從而實現更高的效能與超頻潛力。這項技術代表了克服 3D 整合中熱牆障礙最有希望的解決方案之一。

(資料來源: Vytautas Navikas/EPFL)

4.4 總結

縱觀整個封裝層級,產業正匯聚於混合式解決方案 (hybrid solutions),這證明了獲勝的策略在於最佳化 (optimization),而非追求單一技術的純粹性。

在系統層級 (system level),異質整合本身就是一種混合方法,混合了來自不同製程節點的小晶片

在互連層級 (interconnect level),像 Intel 的 EMIB 這樣的技術,是高密度矽橋接器與低成本有機載板的混合體,兼具兩者之長。AMD 的 MI300 架構,將 3D 堆疊的運算晶粒置於搭載 HBM 的 2.5D 基礎晶粒之上,是另一個混合 2.5D/3D 架構的極佳範例。

在材料層級 (material level),我們看到了嵌入有機中介層的矽橋接器,以及混合金屬-有機散熱蓋 (hybrid metal-organic heat spreaders) 的發展

這表明主導的哲學並非是讓矽「戰勝」有機材料,或讓 2.5D「戰勝」3D,而是在絕對必要的地方(例如晶粒間的互連介面)使用最先進、昂貴的解決方案,並在系統的其他部分利用更具成本效益的技術。這種務實的、混合的方法是平衡 PPAC (功耗 Power、效能 Performance、面積 Area、成本 Cost) 的關鍵。

關於 DNN Technology

總部位於台灣,DNN Technology 是半導體設備與全方位解決方案的全球領導者,專注於二手半導體設備交易 (Used Equipment Trading)、實驗室與無塵室系統建置 (Laboratory and Cleanroom Systems Construction) 以及技術顧問服務。

憑藉超過二十年的產業經驗與由三十多位資深技術專家組成的團隊,DNN Technology 已在五十多個國家成功執行專案,致力於提供客製化、創新且高效的解決方案。