2026 先進封裝指南(五):半導體供應鏈 CPO、KGD 與 Chiplet 趨勢解析

回顧 本指南系列的前四部分,已經為後摩爾定律時代的半導體產業描繪出了演進的藍圖

|

前言

在這最後一期的連載中,我們將把視野從技術細節提升至戰略展望。

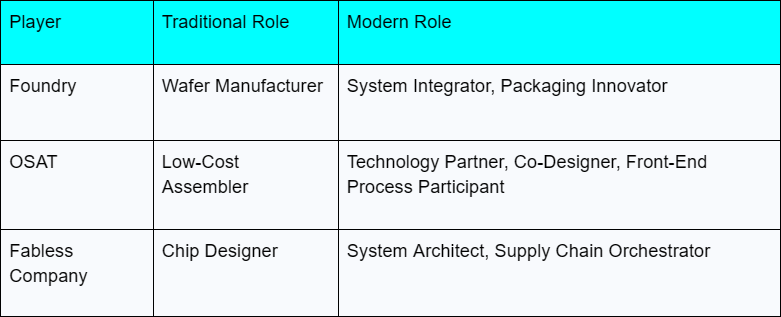

本文將深入探討由小晶片所引發的商業轉型,分析晶圓代工廠、委外封測代工廠與無晶圓廠設計公司在重塑後的供應鏈中所扮演的新角色。

接下來,我們將展望定義下一代系統級封裝 (System-in-Package, SiP) 的未來趨勢,包括共同封裝光學 (Co-Packaged Optics, CPO) 與晶圓級整合 (wafer-scale integration) 等關鍵技術。

最後,我們將審視那些持續存在的根本性挑戰——從確保已知良裸晶 (Known-Good-Die, KGD) 到克服散熱管理的物理極限——這些都是實現異質整合全部潛力的關鍵所在。

5.1 晶圓代工、OSAT 與 Fabless 在分拆架構時代的新角色

小晶片時代的核心悖論在於:雖然技術上是將單體式晶片進行拆解,但這反而以一種前所未有的力道,迫使半導體供應鏈在策略與營運層面上進行再整合

傳統的線性模式 (linear model)——即設計公司將設計移交給晶圓代工廠 (Foundry),然後再轉交給委外封測代工廠 (OSAT)——如今已顯過時。

取而代之的是一個高度協作且複雜的網絡。在這個新模式中,封裝技術的選擇不再只是後段製程 的最後一步,而是一個必須在設計階段之初就做出的核心架構決策

5.1.1 晶圓代工廠:系統整合者的崛起

領先的晶圓代工廠已不再滿足於僅僅製造晶圓;他們正透過垂直整合,轉型成為系統級解決方案 的供應商。

他們將先進封裝視為一項關鍵的差異化優勢,用以吸引並留住高價值的客戶,特別是在 AI 與高效能運算 (HPC) 領域。

- 台積電的CoWoS 主宰地位

為了滿足來自 NVIDIA 與 AMD 等客戶的巨大需求,台積電 (TSMC) 正積極擴充其 CoWoS (Chip-on-Wafer-on-Substrate) 封裝產能

預測顯示,其月產能將從 2024 年的約 35,000 片晶圓,飆升至 2025 年底的 70,000 至 90,000 片,並有潛力在 2026 年達到 130,000 片

此次擴充計畫涵蓋了位於台南 (AP8)、竹南 (AP6B)、嘉義以及台中 (AP5B) 的新建與擴建廠房。這項策略創造了一個具有高度黏著度 (sticky) 的生態系,客戶對先進封裝產能的依賴程度,如今已與其對最新製程節點 (process nodes) 的需求同等關鍵

- Intel 的系統晶圓代工策略

Intel 將其 Foveros (3D) 與 EMIB (2.5D) 技術視為其 IDM 2.0 策略的基石。其在新墨西哥州 (New Mexico) 廠房投入的 35 億美元巨額投資,正是致力於推進 Foveros 3D 封裝技術的發展

Intel 的技術組合——包含了 Foveros-S (採用矽中介層)、Foveros-R (採用 RDL 扇出層)、與 Foveros-B (採用矽橋接器),以及混合式的 EMIB 3.5D 架構——將該公司定位為正在經歷一場轉型:從單純的晶片製造商,進化為「晶片系統 (Systems of Chips)」的供應商

- 三星的多樣化產品組合

三星正以其多樣化的 「Cube」封裝系列,挑戰台積電的領先地位。該系列包括:I-CubeS (採用全矽中介層)、I-CubeE (採用嵌入式矽橋接器),以及更具成本效益的 I-CubeR (採用全有機 RDL 中介層)

這種分層式的產品策略 (tiered product strategy) 讓三星能夠針對不同的市場區隔提供最佳性價比 (cost-performance) 的解決方案——從最頂級的 AI 加速器,到對成本敏感的邊緣運算裝置皆能涵蓋

與此同時,三星也正在進行鉅額投資,包括計畫在美國投資 70 億美元建立一座先進封裝廠,以及在日本設立研發中心。其目標是打造一個從設計、製造到封裝的完整一站式服務 (one-stop service)

5.1.2 OSATs:躍升為關鍵技術合作夥伴

傳統上被視為提供低成本組裝服務的委外封測代工廠,如今正積極向價值鏈上游移動。

它們已不再僅是單純的代工者,而是轉型成為不可或缺的技術合作夥伴,以及推動產業創新的關鍵參與者

- 日月光 (ASE) 與 Amkor 的深度合作關係

為了與晶圓代工廠提供的整合解決方案競爭,OSAT 業者正積極開發自有的先進封裝平台(如日月光的 FOCoS),並展開前所未有的深度合作。

其中最具指標性的趨勢是,受 AI 晶片需求激增的驅動,台積電 (TSMC) 首次決定將其前端的 Chip-on-Wafer (CoW) 製程外包給日月光旗下的子公司矽品精密。

此舉代表了對日月光技術能力的重大認可,因為 CoW 製程比傳統上由 OSAT 處理的後段 Wafer-on-Substrate (WoS) 製程更為複雜且獲利更高。

- 打造美國本土生態系 (Amkor 與 TSMC 在亞利桑那州的合作)

Amkor 與 台積電 (TSMC) 在亞利桑那州的合作,是建立具備韌性且端到端的美國本土供應鏈的一個里程碑。

Amkor 正斥資 70 億美元在亞利桑那州皮奧里亞 打造大型園區,旨在提供一站式的先進封裝與測試服務——其中涵蓋了台積電的 InFO 與 CoWoS 技術——專門處理台積電鄰近鳳凰城 晶圓廠所生產的晶圓。

這種地緣上的鄰近性旨在縮短產品週期時間,並為 Apple 與 NVIDIA 等關鍵客戶提供在地化的供應鏈支援

5.1.3 無晶圓廠 (Fabless):系統的架構師

無晶圓廠設計公司已不再僅僅是晶片設計者;他們現在是完整多晶片系統的架構師,並且已經躍升為推動封裝創新的主要驅動力。

- NVIDIA 的 Blackwell 架構:

B200 GPU 正是這一趨勢的最佳典範;它採用了雙小晶片 (dual-chiplet) 設計,並將其整合於單一封裝之中

這兩顆小晶片透過客製化的 10 TB/s 高速互連技術連接,使其能作為一顆單一且具備快取一致性的 GPU 來運作

這種複雜的設計,基於台積電 (TSMC) 的 4N 製程與 CoWoS 封裝技術,直接定義了整個製造供應鏈的技術規格需求

- AMD的 MI300 系列

MI300 系列展示了一種混合 2.5D/3D 的架構。其 GPU 與 CPU 小晶片(分別稱為 XCD 與 CCD)採用 台積電 (TSMC) N5 製程製造,並以 3D 堆疊的方式置於採用 6nm 製程製造的 I/O 晶粒 (IODs) 之上

接著,這個完整的 3D 堆疊結構會被放置在 2.5D 矽中介層上,並與 HBM3 記憶體堆疊並排部署。這種先進的「3.5D」方法,充分體現了當今無晶圓廠設計公司所追求的極致系統級最佳化

5.1.4 再整合

小晶片 (Chiplets) 的基本前提是將大型、單體式 SoC 拆解成多個更小、更專業化的晶粒。這似乎指向一個更模組化、可互換的未來。然而,最終的系統級封裝 (SiP) 的效能,卻極度依賴這些小晶片之間的實體互連

封裝技術的選擇(例如 CoWoS 或 EMIB)及其物理特性(例如凸塊間距 bump pitch、RDL 線寬/線距),會直接影響並限制小晶片本身的 I/O 設計

這種相互依賴性意味著小晶片與封裝無法孤立設計。像 NVIDIA 這樣的無晶圓廠公司不能簡單地設計好 GPU 晶粒然後丟過牆給台積電。GPU 小晶片的設計與 CoWoS 封裝的架構,必須從專案的一開始就透過深度合作進行協同設計 (co-designed)」與共同最佳化 (co-optimized)

這種對協同設計的需求,粉碎了傳統上無晶圓廠設計、晶圓代工製造與 OSAT 封測之間僵化的界線。如今,晶圓代工廠深入參與封裝設計與組裝;OSAT 業者被引入前端製程;而無晶圓廠公司反過來推動著封裝技術的發展藍圖

因此拆解晶片的行為,反而自相矛盾地迫使供應鏈中的所有參與者,在營運、策略與設計流程上比以往任何時候都更緊密地再整合 (re-integrate)。這正是大整合 (Great Re-integration) 時代的黎明

5.2 後微縮技術:CPO 與晶圓級整合

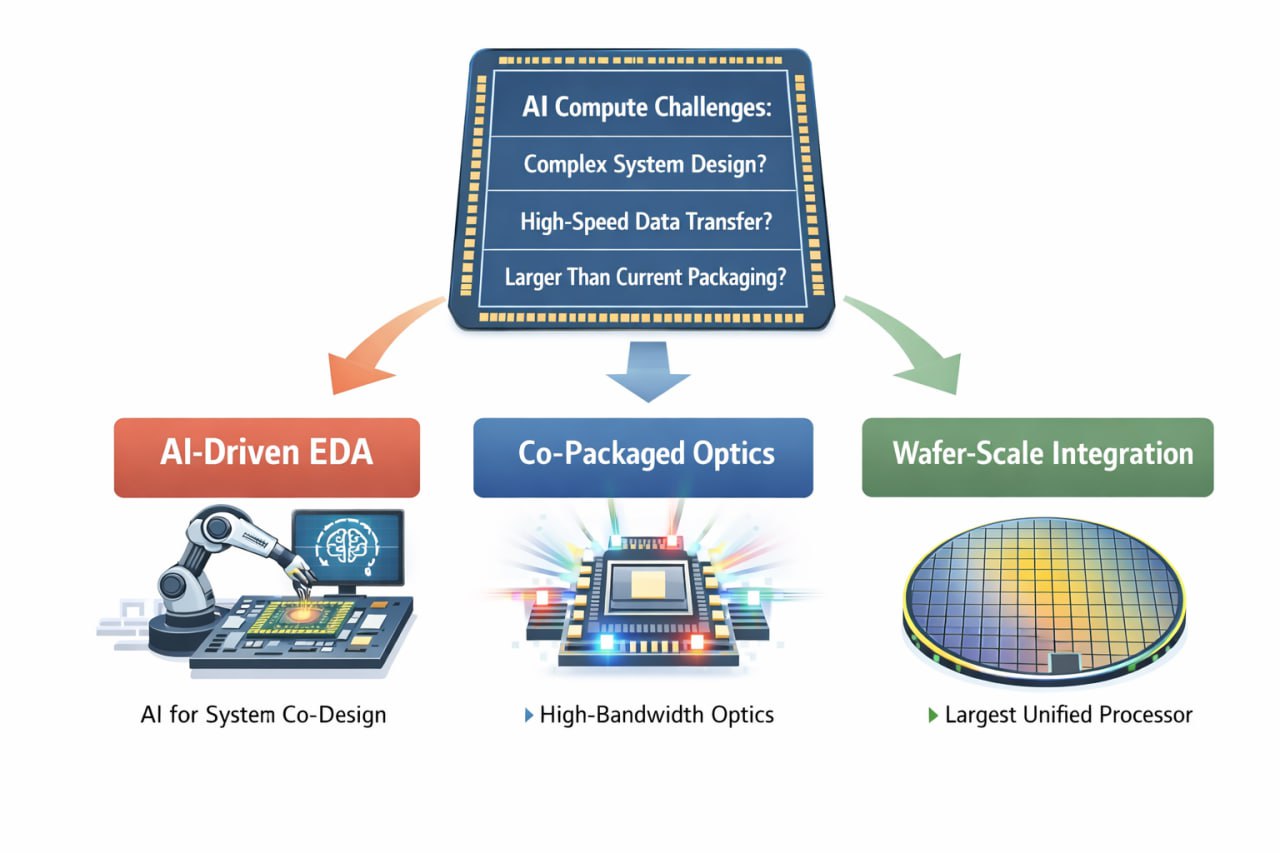

本節將探討下一波的封裝創新,其範圍將超越目前的 2.5D 與 3D 典範。這些技術旨在解決未來的瓶頸,特別是與電訊號傳輸的極限、晶片尺寸以及設計複雜度相關的挑戰。

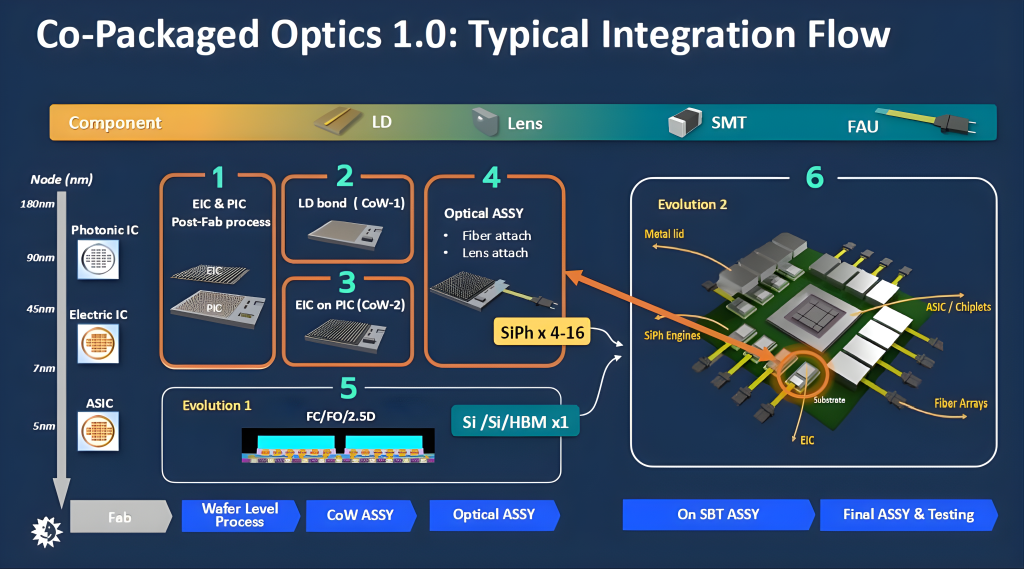

5.2.1 共同封裝光學 (CPO):突破電訊號傳輸瓶頸

隨著 AI 叢集 (AI clusters) 與資料中心的資料傳輸速率呈指數級成長,傳統銅導線互連的功耗問題與頻寬限制,正日益成為系統級效能的主要瓶頸。

共同封裝光學 (CPO) 技術旨在解決此問題,其核心策略是將矽光子引擎直接與電子特定應用積體電路 (ASICs) 整合在同一個封裝內。這種架構實現了以光為基礎的通訊,不僅帶來了頻寬密度的巨大躍進,更能將功耗大幅降低 30% 至 50%。

CPO 市場正處於爆發性成長的前夕,預計規模將從 2025 年的約 20 億美元,擴張至 2033 年的超過 250 億美元,年均複合成長率 (CAGR) 高達 40%。資料中心的大規模部署預計將在 2028 年至 2030 年間發生。包括 Broadcom、Cisco、Intel 與 NVIDIA 在內的產業巨擘皆已在此領域投入鉅資,視 CPO 為實現未來高效能網路與運算的關鍵技術。

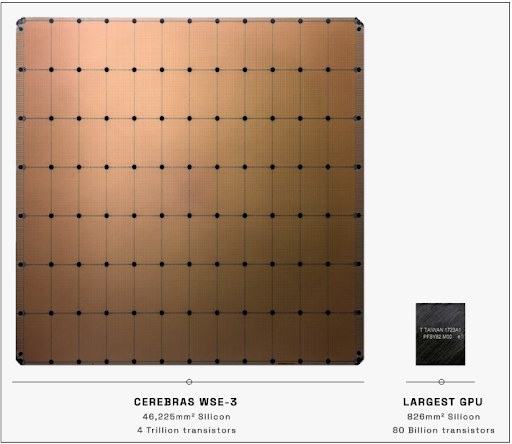

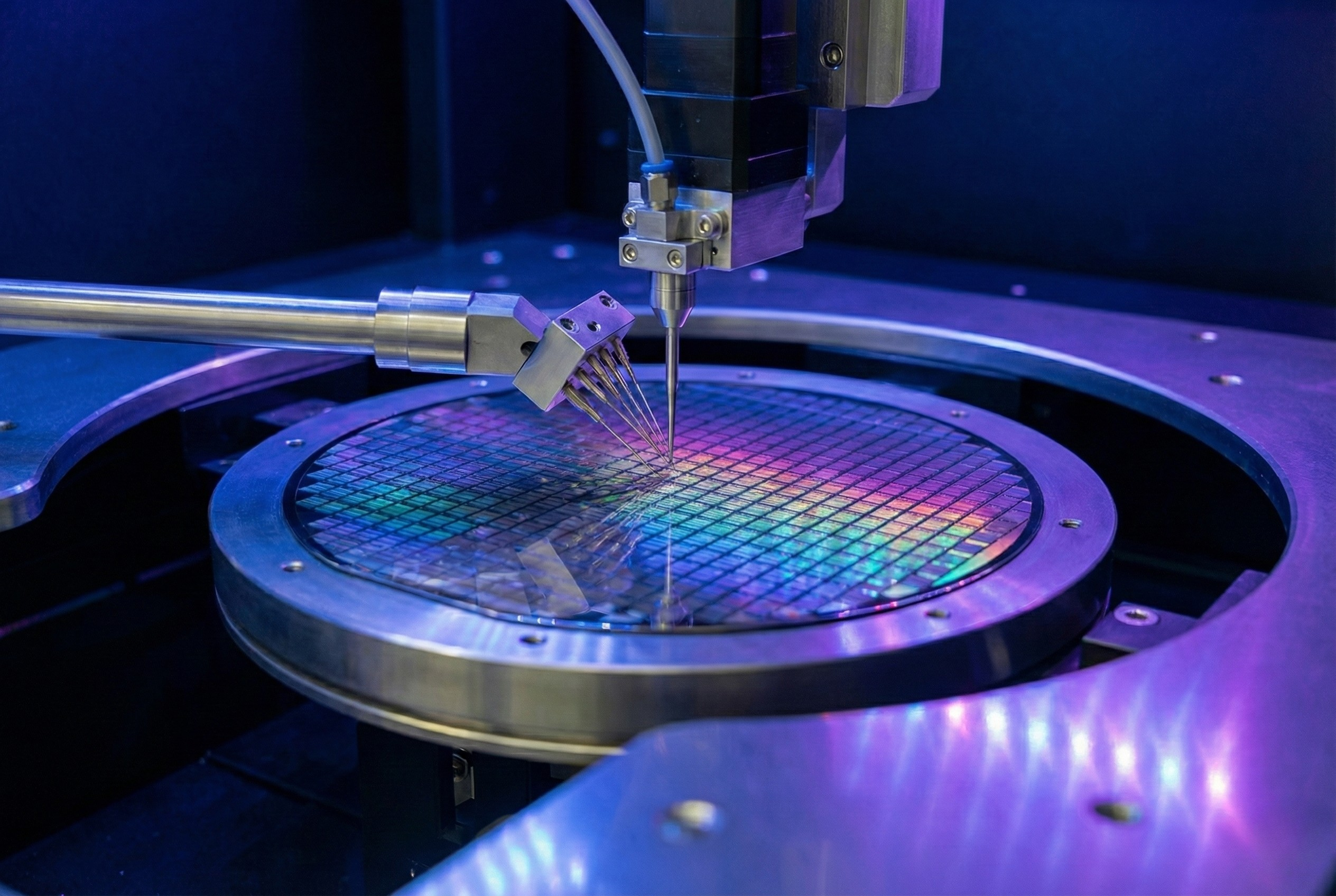

5.2.2 晶圓級整合

晶圓級整合 (Wafer-scale integration) 代表了 2.5D 整合技術最極致的展現形式。不同於將晶圓切割成個別的晶片,它直接利用整片 300mm 晶圓作為一顆單一、巨大的超級晶片,從而完全消除了傳統晶片之間的物理界線。

- 案例研究: Cerebras WSE-3

Cerebras Systems 推出的第三代晶圓級引擎 (WSE-3) 正是此概念的巔峰之作。它是一個基於台積電 (TSMC) 5nm 製程打造的單一運算單元 (single processing unit),搭載了驚人的 4 兆個電晶體、90 萬個 AI 最佳化核心,以及 44GB 的片上 SRAM (on-chip SRAM)

- 運算與記憶體的解構

Cerebras 架構的一項關鍵創新,在於將晶圓上的運算單元與外部記憶體進行解構。WSE-3 透過高速互連技術連接至名為 MemoryX 的外部記憶體系統,其容量可擴充至驚人的 1,200 TB。

這使得單一台 CS-3 系統就能儲存並訓練高達 24 兆參數的 AI 模型——這項任務在過去通常需要由數千個 GPU 組成的龐大叢集才能完成。

這種架構從根本上解決了 GPU 設計中固有的記憶體容量限制,亦即 HBM 記憶體必須與運算晶粒緊密耦合 (tightly coupled) 所帶來的瓶頸。

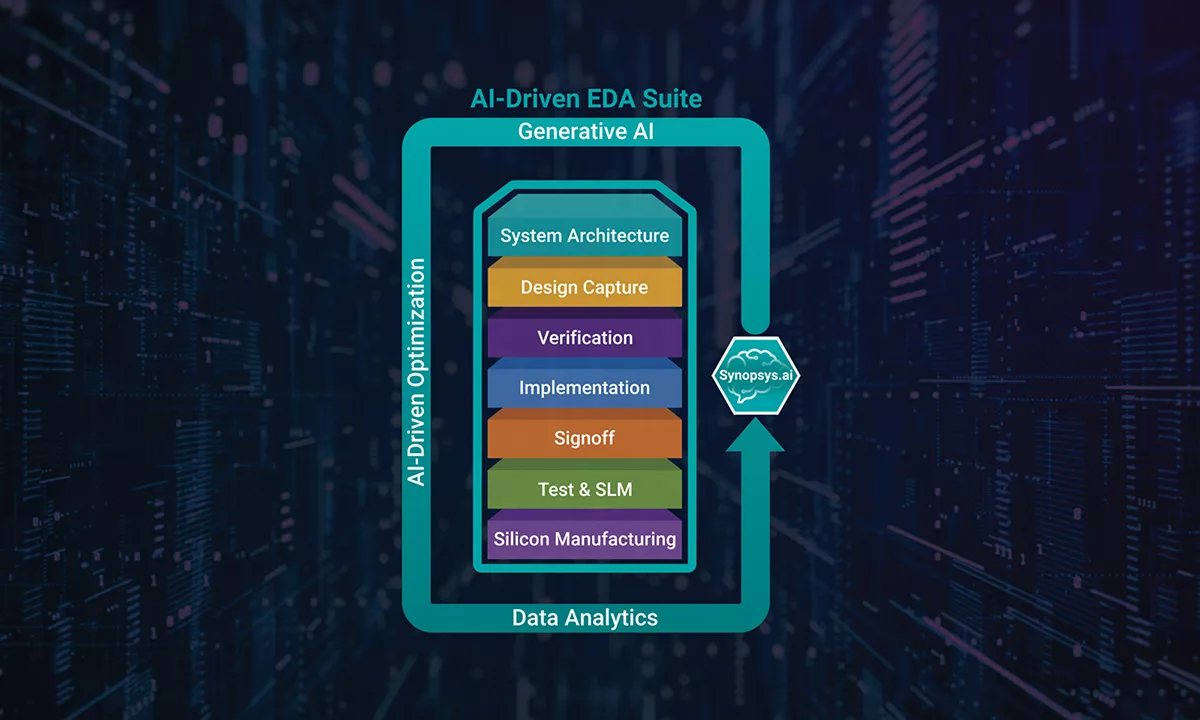

5.2.3 AI 驅動設計

多晶粒系統的設計空間之大猶如天文數字,這使得要透過人工方式來對其切割、佈局與多物理場分析 進行最佳化,變得完全不切實際

- Synopsys.ai

Synopsys 是此領域的領導者。其 Synopsys.ai 套件中的工具——如 3DSO.ai 與 3DIC Compiler——利用 AI 來自動化並最佳化多晶粒設計流程

一個關鍵的客戶成功案例顯示,3DIC Compiler 在應用於三星的 I-CubeS 技術時,成功將 HBM3 佈線時間從數天大幅縮短至僅僅 4 小時,並將整體的設計週期縮短了 10 倍

此外,Synopsys.ai Copilot 利用生成式 AI 進一步加速了如 RTL 生成與驗證等工作流程。

- Cadence Cerebrus AI Studio`

Cadence 的平台採用了代理式 AI (Agentic AI) 技術來協調編排整個 SoC 實作流程,這讓單一位工程師就能夠同時管理多個區塊的設計工作。

在與三星奧斯汀研發中心 (SARC) 的成功合作案例中,該平台在一個 SoC 子系統上實現了 4 倍的整體生產力提升,並同時帶來了 8% 至 11% 的

5.2.4 相互依存的解決方案

我們必須體認到,AI 運算的需求正以指數級速度成長,其速度遠遠超越了傳統製程微縮所能提供的效能增益。這迫使設計者必須採用小晶片 (chiplets) 來建構更大、更複雜的系統——例如 NVIDIA Blackwell 與 AMD MI300 正是這種架構解決方案的代表

然而,這種架構解決方案也衍生出了三個全新的重大瓶頸:

(A) 您該如何設計如此複雜的系統?

(B) 您如何讓資料進出該系統的速度夠快?

(C) 如果您需要的系統規模,比目前封裝技術所能容納的極限還要大怎麼辦?

這三個未來前沿並非獨立的研究路徑,而是一套緊密耦合且共同演進的解決方案套件,旨在維持 AI 算力的發展軌跡:

AI 驅動的 EDA 是針對 瓶頸 (A) 的直接解答:因為系統複雜度已超越人類能力的極限,必須仰賴 AI 來管理多物理場協同設計與佈局規劃

共同封裝光學 (CPO) 是針對 瓶頸 (B) 的直接解答:因為電子 I/O 已觸及功耗與頻寬的物理極限,必須引進光子技術來餵養這頭運算巨獸

晶圓級整合 則是針對 瓶頸 (C) 的直接解答:它代表了 2.5D 整合的邏輯極致,旨在打造出最大可能的單一處理器,並將晶片間的通訊延遲降至最低

總結來說,若沒有 AI 驅動的工具,您無法設計出晶圓級引擎;若沒有光學互連,您也無法將多個此類系統連接成超級電腦。它們是支撐 AI 硬體未來的三大支柱,缺一不可

5.3 鐵律:持續存在的物理與經濟挑戰

本節將深入探討那些構成先進封裝創新主要制約的根本性且反覆出現的挑戰。這些問題並無法被一勞永逸地解決,而是需要我們與物理定律及經濟法則進行一場持久戰

5.3.1 已知良裸晶 (KGD) 測試

小晶片系統的核心經濟原則在於:單一顆有缺陷的小晶片(成本可能僅數百美元),就足以導致整個 SiP (系統級封裝)(價值數千美元)完全報銷。這種財務風險會隨著封裝內小晶片的數量呈指數級增加

如果一個封裝包含 n 顆小晶片,且每一顆的良率 為 Y,則最終封裝的良率大約為 Y 的 N 次方。舉例來說,即便單一顆小晶片的良率高達 95%,對於一個包含 5 顆小晶片的封裝,其整體良率會下降至 77%;而對於一個包含 10 顆小晶片的封裝,良率更會驟降至僅剩 60%

這使得已知良裸晶 (Known-Good-Die, KGD)測試——即在組裝前確保每一顆裸晶皆功能完備——成為最關鍵的經濟挑戰。然而,探針卡 的高昂成本,以及在晶圓層級執行全速測試的技術難度,使得要達到 100% KGD 覆蓋率的成本變得極其高昂且令人望而卻步

- 測試標準化

為了應對測試挑戰,產業界正轉向採用如 IEEE 1838(三維堆疊積體電路測試存取架構標準)這類的規範。該標準定義了一種以晶粒為中心的測試架構,其中包含了 晶粒封裝暫存器 (Die Wrapper Register, DWR) 與測試電梯等功能機制,以確保個別晶粒及其互連線路無論在堆疊前還是堆疊後,皆能進行測試。

這為多供應商生態系中的互通性 (interoperability) 與可測試性 (testability),提供了一個通用的框架。

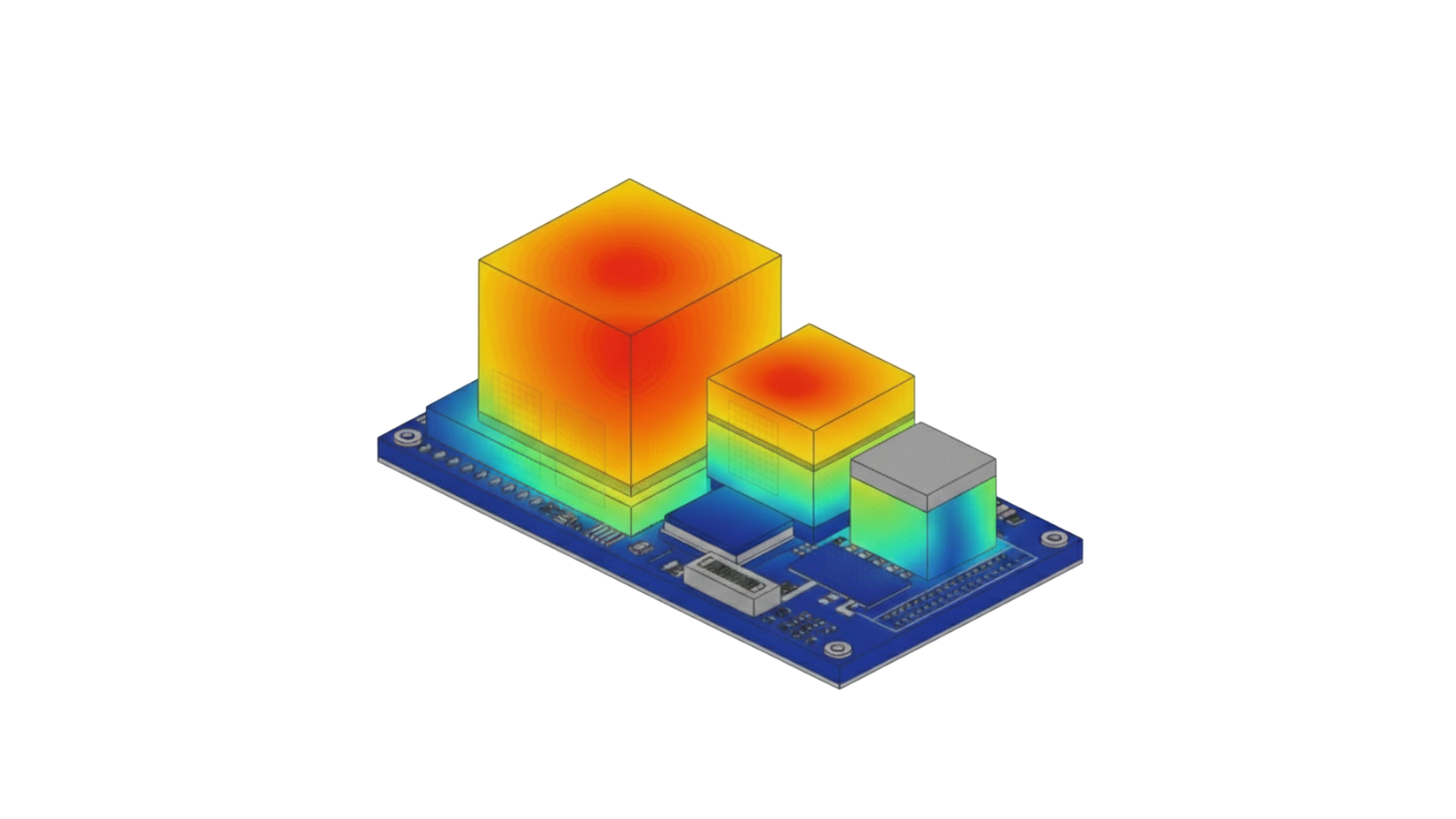

5.3.2 KGD:熱挑戰的經濟體現

已知良裸晶 (KGD) 問題的核心在於,單一顆故障的晶粒就會導致整個多小晶片封裝報廢。這是一個關於良率損失 (yield loss) 的經濟問題。然而,導致晶粒在組裝後失效的主要原因之一,正是熱機械應力

當封裝在運作過程中升溫時,熱膨脹係數 (CTE) 不匹配會導致翹曲與應力,隨著時間推移,這可能導致如錫球裂紋等互連結構的失效

因此,一顆通過了初始晶圓級測試的已知良裸晶,一旦被整合進封裝中並承受其在單獨狀態下從未經歷過的應力時,仍可能會失效

這意味著 KGD 問題不僅僅是找出既有的製造缺陷,更關鍵的是,要能夠預測哪些晶粒在最終封裝系統的熱與機械應力下將會變成瑕疵品

這種預測需要複雜的多物理場模擬(這正是本指南 Part 4 的重點)。設計者必須模擬耦合的電-熱-力回饋迴圈,以便在製造前就識別出高應力點與潛在的失效模式。從這個角度來看,KGD 的經濟問題與熱管理的物理問題,其實是一體兩面

因晶粒失效而報廢封裝所帶來的財務風險,直接就是我們無法完美預測並減輕熱機械應力物理效應的經濟後果。因此,提升 KGD 良率與提升我們在多物理場協同設計及熱管理方面的能力,是密不可分的

5.3.3 熱牆:極致密度下的熱管理

談到熱管理,散熱無疑是先進封裝中最終極的物理瓶頸。在 3D 堆疊與高密度 2.5D 系統中的功率密度 是如此極端,以至於要從僅僅幾平方公分的面積中移除數百瓦的熱量,是一項艱鉅的巨大挑戰。

- 失效物理機制 (CTE不匹配)

一個普遍存在的可靠度挑戰源於不同材料之間的熱膨脹係數 (CTE) 不匹配所引發的熱機械應力。矽晶粒 (CTE 約 3 ppm/°C) 的膨脹與收縮速率,遠低於有機載板 (CTE 約 17-50 ppm/°C)。

這種差異會導致封裝在溫度循環期間發生翹曲,進而引發災難性的失效,例如焊點破裂與分層。這正是本指南 Part 4 所強調的多物理場協同設計之所以如此不可或缺的根本原因。

- 先進熱介面材料 (TIMs)

產業界正從傳統的散熱膏,轉向更先進的金屬基熱介面材料。這些材料包括具有高熱導率 (約 86 W/mK) 的焊料型 TIMs 、液態金屬,以及可壓縮式 TIMs(例如 Indium Corporation 的 Heat-Spring®)。這些材料對於高效能 AI 加速器中的 TIM1 與 TIM1.5 應用至關重要。

- 液冷技術的未來 (微流體冷卻)

面對最極端的熱挑戰,特別是在熱量容易滯留於層間的 3D 堆疊結構中,傳統的氣冷技術已不敷使用。未來的趨勢在於直接液冷技術。來自 Microsoft 等公司的前瞻研究已展示了微流體冷卻技術,即將微小的通道直接蝕刻在矽晶粒的背面。

這讓冷卻液能直接流經晶片內部,其熱移除效率比先進的水冷板高出 3 倍,從而釋放更高的效能與超頻潛力。

5.3.4 生態系標準化

此外,正如我們在前一章所討論的,要實現真正開放、「隨插即用 (plug-and-play)」 的小晶片市集願景,完全取決於是否擁有穩健且被廣泛採用的標準。

- UCIe 的角色

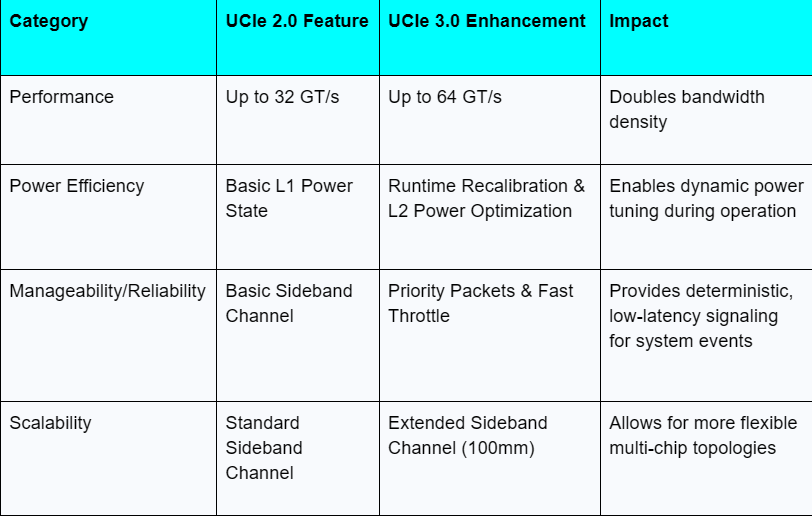

通用小晶片互連快傳 (Universal Chiplet Interconnect Express, UCIe) 是目前最關鍵的標準,其目標是成為小晶片界的 USB。它定義了完整的晶片對晶片通訊規格,範圍涵蓋了從實體層、協定層一路到軟體堆疊。

- UCIe 3.0 規範

於 2025 年 8 月發布的 UCIe 3.0 規範代表了一次重大的技術飛躍。它將最大資料傳輸速率翻倍至 64 GT/s,並透過運行時重新校準與 L2 電源狀態優化等功能,進一步增強了能源效率

此外,它也提升了系統管理能力,新增了包括擴展至 100mm 的邊帶通道、優先級封包,以及快速降頻/緊急關機機制。至關重要的是,它與先前版本完全向下相容

儘管 UCIe 3.0 邁出了巨大的一步,但要建立一個包括互通性驗證、供應鏈安全以及明確的責任歸屬商業模式在內的完整基礎設施,以實現一個可信賴的、多供應商生態系,仍是一項需要數年時間才能完全成熟的長期任務。

結論:邁向系統級整合的不可逆轉趨勢

本指南系列的五個部分共同描繪了一幅清晰的圖景:摩爾定律的放緩並非終點,而是一個新時代的起點——一個以封裝 為核心的創新時代。

從探討為何先進封裝是必要的,到剖析其各種技術架構,再到分析小晶片 (chiplets) 與異質整合的設計哲學,並深入探究底層的物理挑戰,我們見證了一場深刻的產業變革

未來的運算效能將不再僅由電晶體微縮決定,而是取決於整個系統的整體協同優化設計。新的戰場已轉移至材料科學、多物理場模擬、供應鏈整合,以及開放標準的發展。

最終,那些能成功掌握系統級整合藝術的企業與工程師——即那些能在封裝層級精準平衡功耗、效能、面積與成本 (PPAC) 之間複雜權衡的人——將定義下一代的技術,從艾級AI 運算到無所不在的智慧裝置。

系統級封裝的時代並非即將來臨;它已經到來。

關於歐耀科技

總部位於台灣,DNN Technology 是半導體設備與全方位解決方案的全球領導者,專注於二手半導體設備交易 (Used Equipment Trading)、實驗室與無塵室系統建置 (Laboratory and Cleanroom Systems Construction) 以及技術顧問服務。

憑藉超過二十年的產業經驗與由三十多位資深技術專家組成的團隊,DNN Technology 已在五十多個國家成功執行專案,致力於提供客製化、創新且高效的解決方案。