2026 先進封裝指南(二):2.5D 、3D-IC 與 FOWLP 封裝比較

在本系列的第一部分,我們確立了為何先進封裝已成為半導體創新的新前線。現在,我們將焦點轉向如何。

本文將深入探討賦予下一代電子產品動能的核心封裝架構。

我們將探索每種主要技術的技術細節,從傳統 2D 封裝的限制開始,接著進入主宰當今高效能運算領域的強大 2.5D 中介層 (Interposer) 解決方案。隨後,我們將向上構建進入真正的 3D-IC 堆疊世界,並探討高密度整合的另一個關鍵路徑——扇出型晶圓級封裝 (FOWLP)。

2.1 基礎:2D 封裝及其限制

最基本且長久存在的封裝形式是 2D(或稱平面)封裝。在這個傳統模式中,單一矽晶粒 (Die) 通常被貼合在層壓載板 或導線架上,並封裝在保護性的塑膠或陶瓷外殼中。晶粒與封裝外部接腳隨後連接至 PCB的電氣連接,是透過晶粒周邊的打線接合 (Wire bonds) 或簡單的覆晶 (Flip-chip) 配置來實現的。

數十年來,這種方法對絕大多數電子裝置來說已經足夠。然而,對於現今的高效能應用而言,2D 封裝的限制已成為顯著的瓶頸。主要問題在於互連長度。當多個晶片(例如處理器與記憶體)被分開封裝並放置在 PCB 上時,訊號在它們之間傳輸的物理距離相當長。

PCB 上的長線路引入了顯著的延遲 (Latency),增加了功耗(為了驅動訊號跨越該距離),並限制了晶片間的整體通訊頻寬。

此外,在 PCB 上放置多個大型封裝會導致佔用龐大的物理面積,這對於智慧型手機和穿戴式裝置等空間受限的產品來說是不可接受的。隨著對速度、效率和微型化的需求增長,產業被迫尋求 PCB 平面以外的解決方案。

Due to the excessively long interconnect distances between chips.

2.2 跨越鴻溝:2.5D 整合的興起

作為傳統 2D 與全 3D 封裝之間的演進橋樑,2.5D 整合成為解決互連瓶頸的一個強大且務實的方案。

2.5D 的核心概念是透過將多個主動晶粒並排安裝在一個被稱為中介層 (Interposer) 的高密度中間載板上,使它們靠得比在 PCB 上更近。

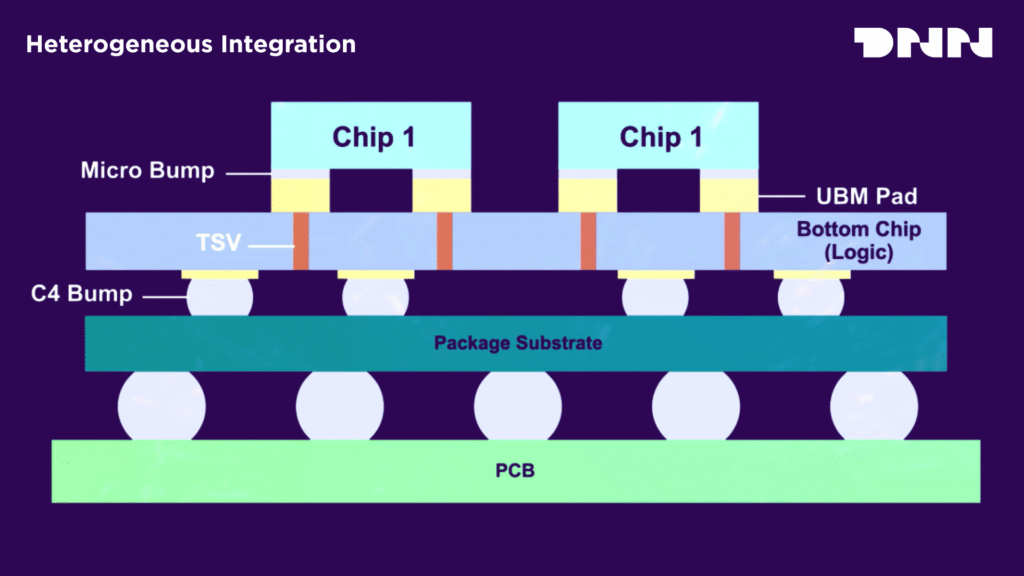

典型 2.5D 封裝的架構是一個多層組件。最上層是主動晶粒(即 Chiplets),例如 GPU 和數個 高頻寬記憶體 (HBM) 堆疊。

這些晶粒透過高密度的微凸塊 (Micro-bumps) 連接至下方的中介層。中介層(通常由矽製成)包含極其精細的重分佈層 (RDLs),負責處理晶粒之間高密度、短距離的水平通訊。

為了將這整個組件連接到主封裝載板,矽中介層利用垂直穿過它的 矽穿孔 (TSVs),將上方的 RDL 連接至其底部表面的較大凸塊網格。

這整個「中介層加晶粒」的組件隨後被安裝在標準的有機封裝載板上,提供與系統 PCB 的最終連接。

這種架構的主要優勢在於大幅縮減了晶粒對晶粒 (Die-to-die) 的互連長度。藉由以中介層上的微觀 RDL 取代 PCB 上的長線路,2.5D 封裝顯著改善了訊號完整性、降低了延遲,並減少了通訊所需的功耗。

這使其成為異質整合的理想平台,允許不同類型的晶片緊密耦合,最顯著的例子就是邏輯處理器與 HBM 的結合,這對現代 AI 和 HPC 系統至關重要。

在當前世代的高效能系統版圖中,2.5D 整合已成為務實的主力技術。

雖然真正的3D 堆疊代表了密度與效能的終極目標,但 2.5D 提供了一個成熟、高良率且熱管理可控的解決方案,直接解決了 AI 與 HPC 中最關鍵的瓶頸:「記憶體牆 (Memory Wall)」。

此術語指的是處理器速度的快速增長與處理器和主記憶體之間資料傳輸速度相對緩慢的改進之間的差距。

將 HBM 堆疊與 GPU 並排在矽中介層上,透過建立兩者之間巨大、超寬且極短的通訊匯流排,有效地粉碎了這道牆。

此外,這種架構比全 3D 堆疊更易於進行熱管理,因為高功率邏輯晶片產生的熱量不會加熱堆疊在其上方的記憶體晶片。在 2.5D 佈局中,發熱元件是相鄰的,為熱量通往冷卻解決方案提供了更直接的路徑。

因此,2.5D 不僅僅是 3D 的「次級」版本;它是針對當今高效能運算中最迫切問題的最佳化、經實戰驗證 的解決方案,專業地平衡了效能增益與可控的熱及製造複雜度。

2.3 向上構建:3D-IC 堆疊的力量

3D-IC 封裝代表了半導體整合的下一個維度,超越了並排排列 (side-by-side arrangements) 的模式,將多個主動晶粒 (active dies) 垂直堆疊。這種架構創造了最短的互連路徑,釋放了前所未有的效能、能源效率與微型化水準。

在 3D-IC 中,兩個或多個經薄化處理的晶粒直接堆疊在彼此之上。這些層之間的電氣連接,是利用穿過矽本身的垂直互連來建立的。

在早期的實作中,這些連接是使用微凸塊製成的,但現今最先進的技術已採用直接銅對銅混合鍵合 (direct Copper-to-Copper (Cu-Cu) hybrid bonding)。

這種先進技術直接融合了兩個晶粒表面的銅墊,創造出一種無縫且高密度的連接。

3D 堆疊的好處深遠,並直接呼應現代電子產品的核心目標,常縮寫為 SWaP (尺寸 Size、重量 Weight 與功耗 Power)。

透過垂直構建,3D-IC 實現了最小的物理佔用空間,這對行動裝置、穿戴式裝置及航太應用至關重要。

這種密度也減輕了重量。最重要的是,極短的垂直互連最小化了寄生電容與電阻,造就了卓越的能源效率,並在堆疊層之間實現了最高的資料頻寬。

從微凸塊 (micro-bumps) 過渡到 Cu-Cu 混合鍵合 (Cu-Cu hybrid bonding) 是一個基礎性的技術飛躍,實現了 3D 整合的全部潛力。微凸塊作為微小的錫球,其排列的緊密程度(即「間距 Pitch」)存在物理限制。

此外,它們還需要在晶粒之間注入聚合物「底部填充劑 (Underfill)」以提供結構支撐,這可能會阻礙熱傳導。

Cu-Cu 混合鍵合 (Cu-Cu hybrid bonding) 克服了這兩項限制。它實現了更細微的互連間距(通常小於 10 微米),大幅增加了單位面積內可容納的連接數量,進而顯著提升 I/O 密度與資料頻寬。

此外,藉由消除焊錫與底部填充劑,它建立了更直接且高效的晶粒間熱傳導路徑,從而改善了散熱效能。

這種直接、細間距的金屬對金屬鍵合是如此無縫,以至於開始模糊了「分離晶片封裝」與「單體式 (Monolithic) 3D 裝置」之間的界線。

正是這項技術變革,將 3D 堆疊從一種利基技術,轉變為未來高效能系統的主流發展路徑。

2.4 比較分析:2D vs. 2.5D vs. 3D-IC

在 2D、2.5D 與 3D 封裝之間的選擇,涉及了效能、成本與複雜度之間一系列複雜的權衡。對於系統架構師與設計工程師而言,理解這些權衡取捨,對於為特定應用選擇合適的技術至關重要。

直接的並排比較 (side-by-side comparison) 為此決策過程提供了一個清晰且有價值的框架。

下表將這些複雜的架構差異提煉為一種易於瀏覽的格式,讓人能快速地分析它們各自的優勢與劣勢。

如表所示,並不存在單一的「最佳」解決方案。

3D-IC 技術提供了效能與整合密度的巔峰,但也伴隨著最高的複雜度與成本,特別是在熱管理方面。

2.5D 整合提供了一種平衡的途徑,在帶來遠優於 2D 的顯著效能增益的同時,仍比全 3D 架構更易於管理,使其成為當今如 AI 加速器等高階系統的標準配置。

對於效能與外型尺寸非首要限制的應用而言,傳統 2D 封裝仍然是最具成本效益的解決方案。封裝技術的未來並非相互取代,而是共存,設計者將根據產品的具體需求,選擇最適切的架構。

2.5 另一條路徑:扇出型晶圓級封裝 (FOWLP)

當 2.5D 與 3D 架構代表著封裝的高效能巔峰時,一個獨特且極為重要的分支也同步發展著:扇出型晶圓級封裝 (FOWLP)。

這項技術提供了一種優雅且具成本效益的方法來實現高密度整合,特別適用於那些無法負擔昂貴矽中介層成本的應用。

FOWLP 的製程與 2.5D 本質上截然不同。FOWLP 並非將晶粒放置在預先製作好的中介層上,而是圍繞著晶粒來構建封裝。在典型的晶片先製流程中,個別晶粒被精確地正面朝下放置在暫時性的載體晶圓 上。接著施加環氧樹脂模塑膠將晶粒包覆,創造出一個新的、較大的重組晶圓

移除載體後,一層或多層重分佈層 (RDLs) 被製作在這個模塑表面之上。這些 RDL 連接晶粒上的銲墊,並在模塑膠表面向外扇出 (fan out),創造出一個新的、較大的 I/O 接觸點陣列,以便放置錫球。

FOWLP 的主要優勢在於其無載板設計。藉由同時省去傳統的層壓載板與矽中介層,它實現了顯著更薄的封裝外型與更低的材料成本。

這種方法提供了卓越的電氣與熱效能,使其成為現代智慧型手機中射頻收發器、電源管理 IC 以及應用處理器 等高產量、成本敏感且空間受限應用的理想選擇。

為了進一步降低成本並提升製造效率,產業正從扇出型晶圓級封裝推進至扇出型面板級封裝 (Fan-Out Panel-Level Packaging, FO-PLP)。

這種演進涉及將製造製程從標準的圓形矽晶圓 ,轉移至大型的矩形面板 (rectangular panels)。面板能同時容納數量更多的封裝單元,最大化製程面積的利用率,並顯著降低單位製造成本與浪費。

FOWLP 在先進封裝的層級中佔據了獨特且至關重要的地位。它提供了一個巧妙的中間地帶,在密度與效能上相較於傳統 2D 封裝有實質性的提升,但又避免了高階 2.5D 系統中所使用的矽中介層之高昂成本與複雜度。

實際上,它是將高密度整合普及化的關鍵技術,讓先進封裝能夠被應用於定義我們日常生活的大眾消費性電子產品 之中。

2.6 總結

半導體設計的工具箱已發生了根本性的擴充。我們見證了 2.5D 整合如何克服 AI 與 HPC 領域中的記憶體牆 ,3D-IC 堆疊如何實現極致的密度與效率,以及 FOWLP 如何為高產量應用提供一條具成本效益的路徑。每一項技術都是針對特定挑戰所精心設計的強大解決方案。

選擇正確的架構是一項關鍵的戰略決策。DNN Technology 的顧問服務 (consulting services) 提供專家級的指引,確保您的專案能建立在最佳的基礎之上。

現在,隨著這些物理平台的確立,我們將進一步探索它們所實現的全新典範。在我們指南的下一部分,將為您介紹:小晶片革命與異質整合的藝術

關於 DNN Technology

總部位於台灣,DNN Technology 是半導體設備與全方位解決方案的全球領導者,專注於二手半導體設備交易 (Used Equipment Trading)、實驗室與無塵室系統建置 (Laboratory and Cleanroom Systems Construction) 以及技術顧問服務。

憑藉超過二十年的產業經驗與由三十多位資深技術專家組成的團隊,DNN Technology 已在五十多個國家成功執行專案,致力於提供客製化、創新且高效的解決方案。