2026 先進封裝指南(一):為何 2.5D 封裝與 Chiplet 封裝是後摩爾定律主流?

前言

半個多世紀以來,半導體產業的進步一直遵循著摩爾定律 (Moore’s Law) 的可預測節奏。然而,隨著電晶體微縮的物理與經濟極限日益明顯,一個新的疆界已經浮現。

現在,通往更高效能、更高能源效率與更多功能的路徑,在於先進封裝 (Advanced Packaging)。本系列的第一篇文章將探討這一根本性的轉變,闡述為何封裝已成為創新的核心。我們將定義您必須了解的核心概念與關鍵術語,並解釋從單一晶片架構的系統單晶片 (SoC) 轉向模組化、多晶片的系統級封裝 (SiP) 的關鍵典範轉移。

1.1 超越摩爾定律:為何封裝成為新前線

摩爾定律所描述的可預測指數級成長,曾是半導體產業半世紀以來的引擎。然而,當電晶體尺寸縮小至原子等級時,量子穿隧效應 (Quantum Tunneling)、散熱問題以及飆升的製造成本已成為難以跨越的障礙。

單純將電晶體做小,已不再是實現更佳效能的最經濟或技術上最可行的途徑。儘管傳統微縮速度放緩,全球對算力的渴望卻未曾削減。相反地,人工智慧 (AI)、高效能運算 (HPC)、5G 通訊以及自駕車系統等變革性技術的興起,創造了對處理能力、資料吞吐量及能源效率前所未有的需求。

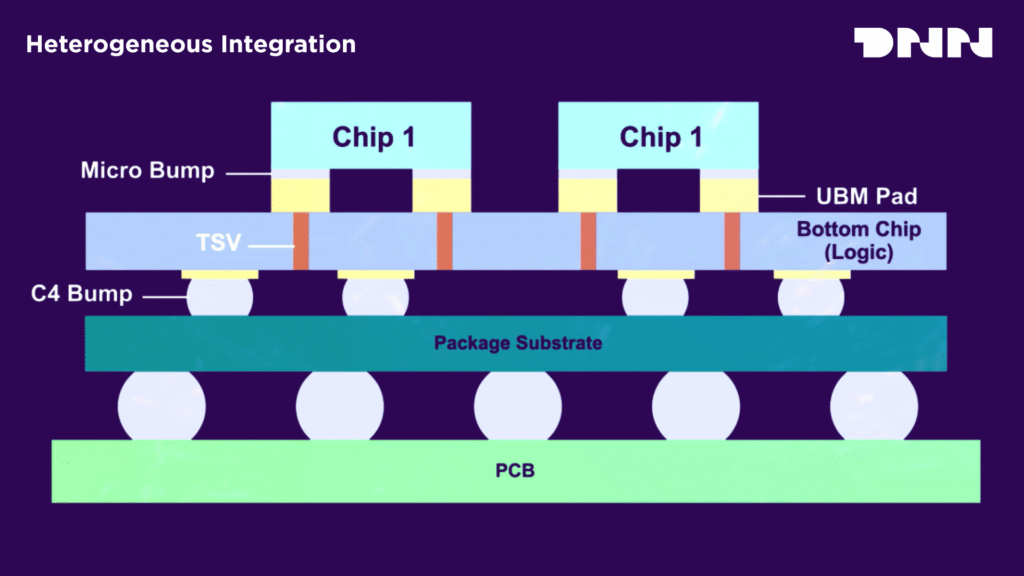

為了填補微縮放緩與需求加速之間的差距,產業已將創新焦點從前段晶圓製造 (Front-end of wafer fabrication) 轉移至後段封裝 (Back-end of packaging)。先進封裝是一系列精密的製程技術,將多個(通常是異質的)半導體晶片整合進單一且高度整合的電子封裝中。

這種方法超越了「單一封裝內僅單一顆晶片」的模式,允許設計者透過高密度的 2D、2.5D 或 3D 配置來排列晶片,從而克服效能瓶頸、降低功耗並減少系統成本。

這一戰略轉向將封裝從過去僅作為保護功能的配角,提升為系統效能的主要驅動力與差異化關鍵。現在的目標不再只是保護矽晶粒 (Die),而是透過優化封裝層級的 PPAC (功率 Power、效能 Performance、面積 Area 與成本 Cost) 方程式,來實現更高層次的功能。在這個新時代,封裝本身已成為創新點,是實現下一代電子產品所需龐大運算能力的基礎。

1.2 封裝詞彙庫:核心概念與術語

要探索先進封裝的複雜領域,首先必須理解其基本組件。這些構建模組及其演進,構成了所有現代封裝架構的基礎。

- Die (晶粒) / Chiplet (小晶片):任何封裝的核心都是 Die,這是從大晶圓上切割下來的長方形半導體材料塊,包含執行特定功能的積體電路。Chiplet (小晶片) 一詞的出現,是用來描述一種特定設計的晶粒——它不單獨運作,而是設計用來在多晶片封裝內與其他 Chiplets 整合,共同組成一個完整的系統。

- Substrate (載板):這是基礎平台,通常是如 FR4 或聚醯亞胺 (Polyamide) 等層壓材料,提供物理結構與電氣路徑,將封裝內的晶粒連接至外部系統(如 PCB印刷電路板)。

Interconnects (互連):這是傳輸電氣訊號與電力的傳導路徑。互連方法已有了顯著的演進:

Wire Bond (打線接合):一種傳統且具成本效益的方法,使用細金屬線將晶粒上表面的銲墊 (Pads) 連接至導線架 (Leadframe) 或載板。此方法受限於線的長度,且連接點只能位於晶粒周邊。

Flip-Chip (覆晶技術):一種更先進的方法,將晶粒「翻轉」倒置。錫球 (Solder balls) 或凸塊 (Bumps) 沉積在晶粒的主動面上,使其能直接貼合在載板上。這允許在晶粒的整個表面進行連接(陣列式排列 Area-array),提供比打線接合更多的 I/O 點以及更短、低電感的電氣路徑。

- Interposer (中介層):2.5D 封裝中的關鍵元件。Interposer 是一個位於主動晶粒與主封裝載板之間的高密度中介層。它作為精密的路由橋樑,提供標準有機載板無法實現的超微細間距 (Ultra-fine-pitch) 互連。Interposer 通常由矽、有機材料或玻璃製成。

- Redistribution Layer (RDL, 重分佈層):這是在晶圓或模塑封裝結構之上製作的額外金屬線路與介電層。其目的是將晶粒上原本的 I/O 銲墊位置「重新路由 (Reroute)」到新的接觸點陣列。這是扇出型 (Fan-Out) 封裝以及在中介層上建立高密度連接的核心技術。

- Through-Silicon Via (TSV, 矽穿孔):一種革命性的技術,建立完全穿過矽晶圓或晶粒的垂直電氣連接。透過將矽本身轉化為互連通道,TSV 是實現 3D 晶粒堆疊 (3D die stacking) 的根本推手,允許垂直堆疊的晶片之間擁有最短的通訊路徑。

歷史演進

這些組件的歷史揭示了一個清晰且一致的敘事:對縮短物理距離的不懈追求。從長距離的周邊打線接合進步到覆晶技術更短的陣列連接,是第一次重大飛躍。下一個瓶頸變成了 PCB 上分離晶片之間的水平距離。

這個問題透過引入 2.5D 封裝中的 Interposer 得到解決,利用 RDL 將晶粒放置得靠得極近,大幅縮短了晶粒對晶粒 (Die-to-die) 的通訊路徑。 最終,3D-IC 技術透過使用 TSV 垂直堆疊晶粒,將這一邏輯推向極致,完全消除了水平距離,實現了絕對最短的路徑。這整個封裝創新的歷史,可以理解為一場透過拉近晶粒距離來對抗訊號傳輸物理限制(延遲與功率損耗)的持續戰鬥。

1.3 系統單晶片 (SoC) vs. 系統級封裝 (SiP):典範轉移

封裝技術的演進促成了設計哲學的根本轉變,從單體式 (Monolithic) 方法轉向模組化 (Modular) 方法。理解 SoC 與 SiP 的區別對於掌握這一變革至關重要。

System-on-Chip (SoC, 系統單晶片):半導體整合的傳統目標。SoC 將完整電子系統所需的所有功能——如處理核心、記憶體、I/O 控制器及類比電路——整合在單一、單體的矽片上。

System-in-Package (SiP, 系統級封裝):相對地,SiP 透過將多個分離的元件整合進單一封裝來實現系統級功能。這些元件可包含一個或多個處理器晶粒、記憶體晶片、感測器及被動元件,全在封裝內互連。任何先進封裝架構——2.5D、3D 或 Fan-Out——都可用來構建 SiP。

產業目前正見證所謂「SoC 趨勢的逆轉」,轉而支持由被稱為 Chiplets (小晶片) 的較小組件構成的模組化、基於 SiP 的架構。這不僅是技術偏好,更是深刻的戰略與經濟決策。

單體式 SoC 方法雖然概念優雅,但伴隨著重大風險與效率低落。它強迫所有系統功能(從高速數位邏輯到敏感的類比 I/O)都在同一種最先進——因此也最昂貴——的製程節點上製造,即使許多功能根本不需要如此先進的技術。此外,大型複雜 SoC 上的一個微小缺陷就可能導致整顆晶片報廢,導致製造良率低落且成本劇增。

使用 Chiplets 的 SiP 方法緩解了這些問題。它將各種系統功能從單一、無容錯空間的製造製程中解耦 (Decouples)。設計者可以為每一顆個別的 Chiplet 選擇最佳的製程節點——例如,高效能 CPU 核心使用 5nm 製程,而類比 I/O Chiplet 則使用更成熟且具成本效益的 28nm 製程。這種「混合搭配 (Mix-and-match)」的能力不僅降低了成本,也顯著提升了整體製造良率。

因為個別的 Chiplets 較小,單一晶片出現缺陷的機率較低。即使出現缺陷,也只需丟棄那顆小的、相對便宜的 Chiplet,而非整個多晶片系統。這種從高風險單體哲學轉向靈活、風險分散的模組化哲學的轉變,是由強大的經濟誘因所驅動,並正在從根本上重塑複雜電子系統的設計與建構方式。

讓歐耀科技推動您的下一代設計

駕馭從單體 SoC 到複雜 SiP 架構的轉變,需要深厚的專業知識與可靠的合作夥伴。邁向 2.5D 與 Chiplet 基礎的設計,涉及製造、材料與系統級整合的關鍵決策。

在 DNN Technology,我們不只了解這些挑戰——我們解決它們。憑藉在 AP Active Interposer (主動式中介層) 設計的豐富經驗以及全套的 Turnkey 顧問服務,我們的團隊已準備好協助您優化 PPAC (功率、效能、面積與成本) 方程式。

立即聯繫我們的專家團隊,討論我們如何能加速您邁入半導體整合新時代的旅程。

關於 DNN Technology

總部位於台灣,DNN Technology 是半導體設備與全方位解決方案的全球領導者,專注於二手半導體設備交易 (Used Equipment Trading)、實驗室與無塵室系統建置 (Laboratory and Cleanroom Systems Construction) 以及技術顧問服務

憑藉超過二十年的產業經驗與由三十多位資深技術專家組成的團隊,DNN Technology 已在五十多個國家成功執行專案,致力於提供客製化、創新且高效的解決方案